# NC2008 Multi Output **Clock Generator IC**

### **Overview**

The NC2008 is a highly integrated multi output clock generator and signal translation device. This design implementation is extremely flexible in providing low noise frequency generation and/ or signal level translation capability. The design architecture incorporates Nineco's second generation analog PLL technology to provide up to 17 output(s) at frequencies ranging from 1Hz to 800 MHz, depending upon the input reference option chosen. One or two external signal sources determine the output characteristics for phase noise and jitter performance for any combination of

performance options of sub 100fs RMS (12 kHz to 20MHz). Configurations can be controlled using I2C interface, external EE PROM or can be pre configured in nonvolatile memory (OTP) at the factory. One or two external signal sources can be accepted from a crystal unit, a single ended LVCMOS signal, a differential (LVDS or LVPECL) signal or a combination of those. When using a crystal unit,

eight differential or 17 single ended clock outputs with output jitter

## Typical Applications

100fs jitter performance is achievable.

- Clock Generation

- Multi output clock buffer

- Signal level translation

ended Low Jitter Clock Outputs Programmable output transmitters (programmable as either 1 LVPECL, 1 LVDS or 2x LVCMOS output)

1Hz to 800 MHz clock output

• Eight differential or up to 17 single

frequency range

- 20 bit divider capability at output transmitters 1-8.

- Low jitter clock outputs of less than .25ps RMS (12kHz to 20MHz) with options for sub 100fs.

- Signal translation from LVCMOS to LVPECL/LVDS or Vice versa

- External EEProm for loading or I2C Interface for system communication

- 3.3V supply

**Features**

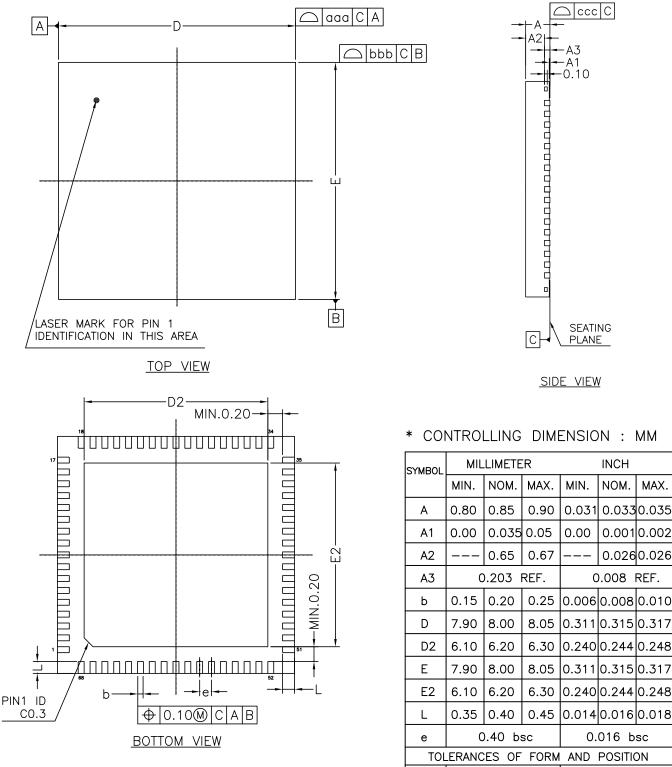

• 8x8 mm 68 pin QFN surface mount package

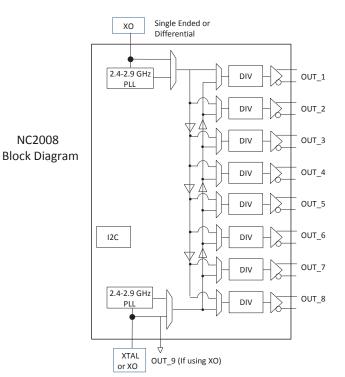

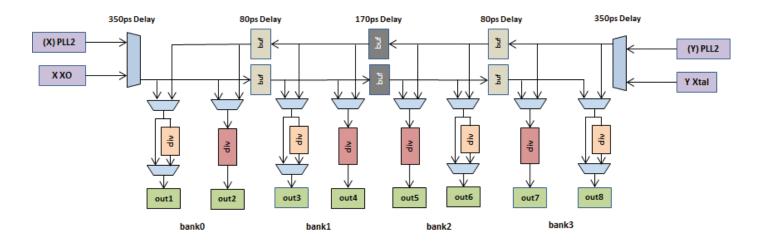

## NC2008 Functional Block Diagram

| Bulletin | TM134       |

|----------|-------------|

| Revision | 03          |

| Date     | 05 Jan 2021 |

Delivering a New Generation of Time and Frequency Solutions for a Connected World.

#### **Specifications**

| Parameter                         | Specification                                                     |

|-----------------------------------|-------------------------------------------------------------------|

| Voltage                           | 3.3V +/- 5%                                                       |

| Power                             | Based on configuration (100ma with outputs tri-stated)            |

|                                   | Outputs add: LVPECL 50ma, LVDS 20Ma, LVCMOS 8 ma                  |

| Temperature                       | -40 to 85 C Industrial temp range operation                       |

| Reference Frequency for PLL       | Crystal unit (40-160MHz), differential (LVDS or LVPECL) signal up |

|                                   | to 800MHz or Single ended clock input 40MHz- 125MHz               |

| Low Jitter Clock Output Frequency | 1 Hz to 800 MHz                                                   |

| Output Transmitter                | Programmable to be either LVPECL, LVDS or 2x LVCMOS               |

| Divider Capability                | 20 bit                                                            |

| Dimensions                        | 8 x 8x 1mm 68 pin QFN package                                     |

#### NC2008 General Description

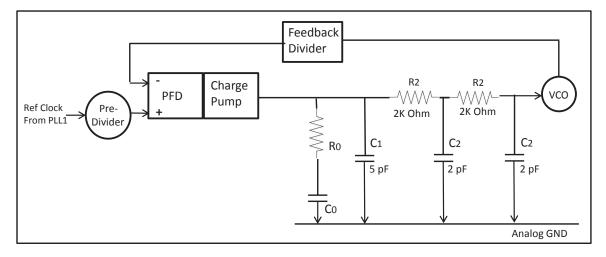

The NC2008 is a highly integrated PLL clock generator ASIC. The design architecture incorporates a sophisticated analog PLL scheme to provide up to 17 low jitter clock outputs at frequencies from 1.5 kHz to 800 MHz from either one or two independent analog integer PLLs. These outputs can be generated from one or two reference input signals at frequencies from 5 MHz to 800 MHz. The reference input signal source can be supported by a crystal, an external single ended LVCMOS clock source, a differential clock source (LVPECL/LVDS) or a combination of these options. The design incorporates two analog PLLs and eight output transmitter circuits, each with 20 bit divider capability. The two PLLs can be used in tandem to share the eight output circuits or all eight can be accessed by one or the other exclusively. Clocks can be generated using the on board oscillator and passed through directly to the output transmitter ports or the input signal can be routed through an APLL with an integrated VCO in the range of 2.4GHz to 2.95 GHz. An internal pre divider makes the usable VCO range of 1.2GHz to 1.475 GHz to be further divided at each individual output transmitter port.

### NC2008 Analog PLL Chain Description

The NC2008 is designed to support two simultaneous, independent frequency domains which share four banks of two clock output stages each. The NC2008 consists of two (2) independent analog PLL stages, referred to as XPLL and YPLL. In each X and Y side, the PLL stage can accept an incoming signal and lock to an internal VCO in the usable range of 1.2GHz to 1.475 GHz. Each of eight output transmitters can be divided by any integer value with up to 20 bit resolution (1048576) to generate clock outputs divided from the VCO frequency chosen. The eight independent programmable clock output transmitter circuits have 3-in-1 programmable output logic capability. Each transmitter circuit can be configured as either 2x LVCMOS outputs, 1 LVDS output or 1 LVPECL output. Depending upon the external XTAL/XO configuration used, clock outputs can be generated in a frequency range from 1Hz to 800MHz (limited to 180MHz for LVCMOS outputs) and can provide output jitter performance of less than 100fs RMS over the integration range of 12 kHz to 20MHz. The two X and Y PLL stages can be used in tandem to share the output stages or independently with all outputs driven from an input from only one side of the chip. There is a fixed skew delay through the output banks of the chip as described below in the Output Transmitter Ports section.

## X-Side PLL Chain Description

On the X side of the chip, XPLL can accept a reference signal input from a single ended LVCMOS signal or differential XO or clock signal at frequencies from 1MHz to 800MHz. For best jitter performance, an XO frequency of 40MHz or higher should be used as an input to the XPLL unless the signal is being passed through to the output transmitters directly. The input frequency enters the chip into a MUX that allows for the signal to be passed directly through to the output transmitters/divider ports or be sent as an input to the XPLL to synthesize output frequencies from the internal VCO divided at the output transmitter ports. Outputs derived from XPLL, depending upon frequency, will generally provide jitter performance levels of < 250fs over the integrated band of 12 kHz to 20 MHz.

| ADDR | NAME      | TYPE | BITS  | DEFAULT | DESCRIPTION         |  |

|------|-----------|------|-------|---------|---------------------|--|

| 0x04 | XPLL Mode | RW   | 2 - 0 | 0       | XPLL Mode           |  |

|      |           |      |       |         | 0, 3: power down    |  |

|      |           |      |       |         | 1: single-end clk   |  |

|      |           |      |       |         | 2: differential clk |  |

PLL Circuit Diagram (X, Y)

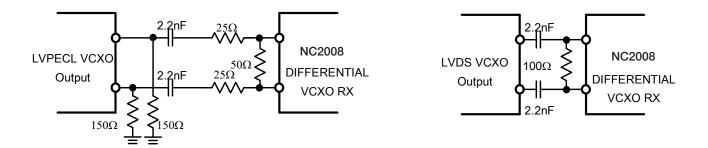

Differential XO termination recommendation in to pins XRX\_P and XRX\_N

NC2008 Data Sheet: TM134 Page 3 Rev: 03 Date: 01/05/2021

#### XPLL BYPASS Mode

The input XO or signal to X side can be passed directly through to the output transmitters/divider ports To bypass the XPLL and send the reference input source to the divider/transmitter ports directly, the XPLL Output Source register setting should be set as "Bypass". A clock signal into the X side reference input will then be passed directly to the output transmitters chosen. Outputs sent to the output ports in bypass mode general retain their jitter character adding minimal jitter.

| ADDRW | NAME               | TYPE | BITS | DEFAULT | DESCRIPTION        |

|-------|--------------------|------|------|---------|--------------------|

| 0x39  | XPLL Output Source | RW   | 0    | 1       | XPLL output source |

|       |                    |      |      |         | 0: Bypass          |

|       |                    |      |      |         | 1: XPLL            |

#### Y-Side PLL Chain Description

On the Y side of the chip, YPLL can be supported by a crystal unit from 10MHz to 170MHz (fundamental mode only) or single ended clock signal at frequencies from 1MHz to 180MHz. For best jitter performance, a crystal or an LVCMOS clock frequency of 40MHz or higher should be used as an input to the YPLL unless the signal is being passed through to the output transmitters directly. An additional output (Output 9) is available when using a single ended XO on the Y side PLL. The XO nominal frequency will bypass directly to Output 9, but with inverted phase, from the input XO (as well as the outputs generated in the transmitter ports when used).

Outputs derived from YPLL, depending upon frequency, will generally support jitter performance levels of < 250fs over the integrated band of 12 kHz to 20 MHz.

| ADDR | NAME      | TYPE | BITS          | DEFAULT | DESCRIPTION   |

|------|-----------|------|---------------|---------|---------------|

| 0x05 | YPLL Mode | RW   | 0             | 0       | YPLL Mode     |

|      |           |      | 0: power down |         | 0: power down |

|      |           |      |               |         | 1: power up   |

#### YPLL BYPASS Mode

The crystal input or the XO/ LVCMOS signal to Y side can be passed directly through to the output transmitters/divider ports To bypass the YPLL and send the reference input source to the divider/transmitter ports directly, the YPLL Output Source register setting should be set as "Bypass". A clock signal into the Y side reference input will then be passed directly to the output transmitters chosen. Outputs sent to the output ports in bypass mode general retain their jitter character adding minimal jitter.

| ADDR | NAME               | TYPE | BITS | DEFAULT | DESCRIPTION        |  |

|------|--------------------|------|------|---------|--------------------|--|

| 0x3a | YPLL Output Source | RW   | 0    | 1       | YPLL output source |  |

|      |                    |      |      |         | 0: Bypass          |  |

|      |                    |      |      |         | 1: YPLL            |  |

#### Eight 3-in-1 Programmable Output Transmitter

Output transmitter ports 1 through output 8 consist of programmable 3-in-1 transmitters that can be configured to output either (2) LVCMOS or 1 LVDS or 1 LVPECL logic signal. Output transmitters can be powered down if not in use. When using LVCMOS mode, outputs can be generated on both output pins (P and N) of the output transmitter, or, one or the other. Polarity of the LVCMOS output at each pin is controllable.

| ADDR | NAME        | TYPE | BITS  | DEFAULT | DESCRIPTION                               |

|------|-------------|------|-------|---------|-------------------------------------------|

| 0x31 | Output1     | RW   | 4 - 0 | 51/102  | Output1 transmitter mode,                 |

|      | Transmitter |      |       |         | Bit[2:0]                                  |

|      | Mode        |      |       |         | 0, 6, 7: power down,                      |

|      |             |      |       |         | 1: LVDS                                   |

|      |             |      |       |         | 2: LVPECL                                 |

|      |             |      |       |         | 3: LVCMOS, P on, N off                    |

|      |             |      |       |         | 4: LVCMOS, P off, N on                    |

|      |             |      |       |         | 5: LVCMOS, P on, N on                     |

|      |             |      |       |         | When transmitter is in LVCMOS mode,       |

|      |             |      |       |         | Bit[5:4] control polarity of output       |

|      |             |      |       |         | Bit4 0: P is not inverse, 1: P inverse    |

|      |             |      |       |         | Bit5 0: N is not inverse, 1: N is inverse |

#### **Output Transmitter Port Description**

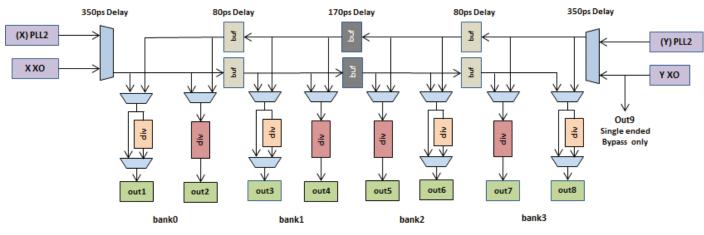

Output transmitter ports 1 through 8 are divided into four output "banks". Each of the four output banks must be controlled as a unit. Bank0 (Output transmitters 1 and 2), Bank1 (Output transmitters 3 and 4), Bank2 (Output transmitters 5 and 6), and Bank3 (Output transmitters 7 and 8) represent four "banks" of outputs that can be controlled independently from each X and Y side of the chip. Either the X side or the Y side of the chip can access all four output banks, thus eliminating the requirement to use both sides X and Y in all applications. However, X and Y side clock signals must access output banks in order and must stop at the first output bank placed in use by the alternate side. For example, if X side uses banks 0, 1 and 2, Y side can only access bank 3 (outputs transmitters 7, and 8) or if Y side uses banks 3 and 2 (output transmitters 8,7 and 6,5), X side can only access bank 1 and 0 (outputs transmitters 1,2 and 3,4).

| ADDR | NAME      | TYPE | BITS  | DEFAULT | DESCRIPTION                                                     |

|------|-----------|------|-------|---------|-----------------------------------------------------------------|

| 0x3b | Output    | RW   | 2 - 0 | 0       | Output 1 ~ 8 source selection, output can come from either xpll |

|      | Source    |      |       |         | or ypll, the arrangement are as follows,                        |

|      | Selection |      |       |         | 0,5,6,7: xpll -> 1,2,3,4,5,6,7,8                                |

|      |           |      |       |         | 1: xpll -> 1,2,3,4,5,6 ypll ->7,8                               |

|      |           |      |       |         | 2: xpll -> 1,2,3,4 ypll -> 5,6,7,8                              |

|      |           |      |       |         | 3:xpll -> 1,2 ypll -> 3,4,5,6,7,8                               |

|      |           |      |       |         | 4:ypll -> 1,2,3,4,5,6,7,8                                       |

Detailed Output Port Diagram (when using an LVCMOS XO on Y side PLL)

Detailed Output Port Diagram (when using a Crystal Unit on Y side PLL)

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NC2008 Data Sheet: TM134 Page 5 Rev: 03 Date: 01/05/2021

## **Output Skew Description**

The skew between clock outputs is constant but will exhibit a cumulative delay relative to each other based on the clock signal traveling through MUXs and Buffers. This will be dependent upon how the output banks are configured from each X and Y side. Delay time are identified in Diagram 1 and 2.

#### Output 9

On the Y side, output 9 has been provided for use when a single ended clock signal is used as the reference input to the Y side PLL or in bypass mode. Output 9 acts as a low jitter buffer that directly bypasses the respective XO signal in and out of the NC2008 resulting in the least amount of additive jitter (about 10fs). This output is intended to be used for ultra-low jitter performance requirements when attempting to retain the characteristics of a low jitter source. If a crystal unit is used as reference source on the Y side PLL, Output 9 is not available since that pin is used as one pole of the crystal unit input. (see Diagram 2)

#### 20 bit Divider Circuits

Output ports 1-8 have 20 bit divider capability (any integer value from 1-1,048,576). Regardless if the frequency is generated by the VCO or if it is bypassed through from the reference input source, the divider circuit can be used to generate divided frequencies. For instance, using a 1MHz input clock source in bypass mode, can achieve a 1Hz output through the divider circuit. Please note, low frequency input options are only available in bypass mode as inputs to the X and Y PLL requires a minimum of 40 MHz input frequency.

| ADDR | NAME     | TYPE | BITS   | DEFAULT | DESCRIPTION                  |  |

|------|----------|------|--------|---------|------------------------------|--|

| 0x40 | Output 1 | RW   | 19 - 0 | 0       | 20 bit OUTPUT1 divider value |  |

| ~    | Divider  |      |        |         |                              |  |

| 0x42 | Value    |      |        |         |                              |  |

#### Symmetry Control for low value odd dividers

Output transmitter circuits #2, 4, 5 and 7 have, by default, output symmetry control when dividing by a single digit odd integer value. In circumstances which require dividing the VCO output frequency by values of 3, 5, 7 or 9, one of these output transmitter circuits should be used to achieve 50/50 duty cycle. When using an odd divider value of greater than nine (9), symmetry control is generally not required to maintain reasonable symmetry in the output. The output ports offering symmetry control do not allow for a direct by-pass through of the reference input frequency and require dividing at the output transmitter circuit by a minimum by 2. Output ports 1, 3, 6 and 8 can by-pass the divider circuit entirely or can divide by any integer number up to the 20bit value.

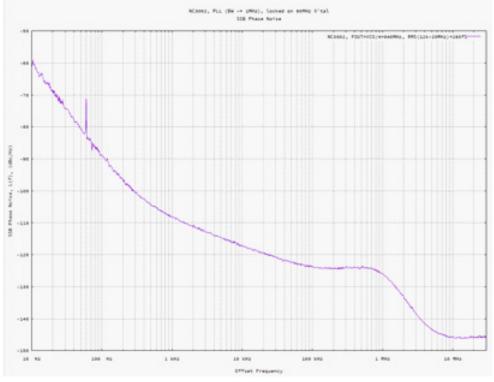

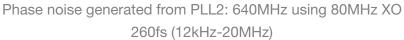

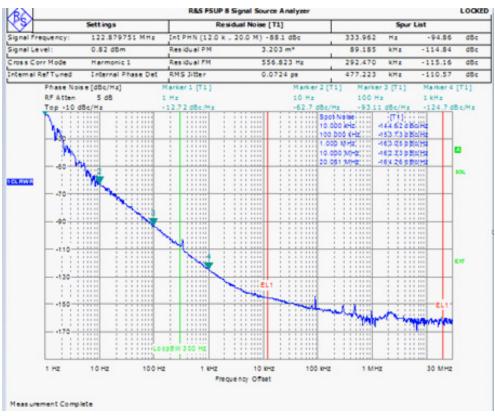

## **Output Phase Noise Characteristics Examples**

Phase noise generated from 156.25MHz Crystals 93fs (q2kHz-20MHz)

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NC2008 Data Sheet: TM134 Page 7 Rev: 03 Date: 01/05/2021

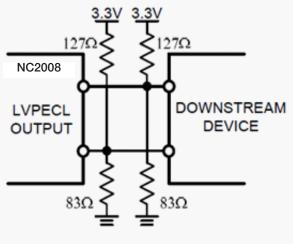

## LVPECL Suggested Termination

DC-Coupled LVPECL Output Driver

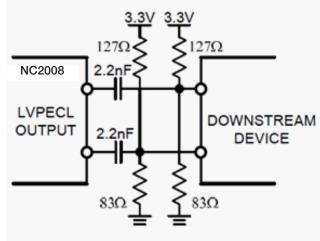

#### AC-Coupled LVPECL Output Driver

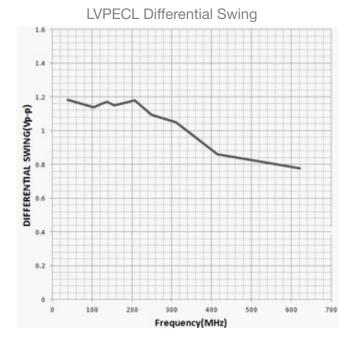

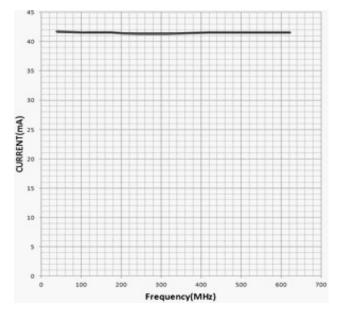

### LVPECL Current Consumption

fvco=1.244GHz, fvcxo=38.88MHz,ftcxo=20MHz

| OUTPUT FREQUENCY<br>(MHz) | DUTY CYCLE (%) | <b>RISE TIME</b><br>(20%~80%)(ps) | CURRENT<br>CONSUMPTION (mA) | DIFFERENTIAL<br>SWING (Vp-p) |

|---------------------------|----------------|-----------------------------------|-----------------------------|------------------------------|

| 38.88                     | 50.09          | 590                               | 41.69                       | 1.183                        |

| 103.681                   | 49.97          | 570                               | 41.59                       | 1.139                        |

| 113.108                   | 45.44          | 560                               | 41.59                       | 1.148                        |

| 124.417                   | 49.98          | 570                               | 41.57                       | 1.161                        |

| 138.239                   | 44.49          | 520                               | 41.53                       | 1.171                        |

| 155.519                   | 49.98          | 530                               | 41.56                       | 1.152                        |

| 177.74                    | 43.06          | 570                               | 41.56                       | 1.163                        |

| 207.362                   | 50.1           | 510                               | 41.41                       | 1.182                        |

| 248.836                   | 42             | 430                               | 41.34                       | 1.095                        |

| 311.054                   | 50.14          | 500                               | 41.32                       | 1.049                        |

| 414.736                   | 35.64          | 370                               | 41.53                       | 0.86                         |

| 622.115                   | 51.05          | 270                               | 41.56                       | 0.778                        |

LVPECL Current Consumption

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NC2008 Data Sheet: TM134 Page 8 Rev: 03 Date: 01/05/2021

Specifications subject to change without notification. See 9co's website for latest revision. © Copyright 2023 9co Not intended for life support applications.

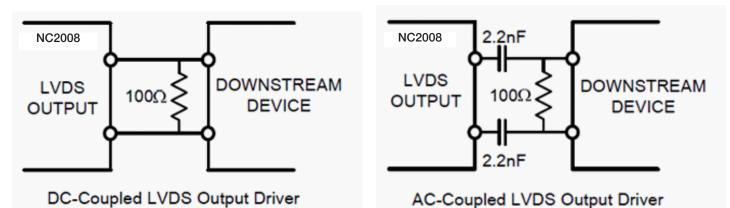

## **LVDS Suggested Termination**

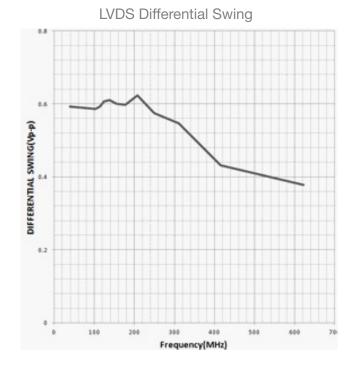

#### **LVDS Current Consumption**

fvco=1.244GHz, fvcxo=38.88MHz,ftcxo=20MHz

| OUTPUT FREQUENCY<br>(MHz) | DUTY CYCLE (%) | <b>RISE TIME</b><br>(20%~80%)(ps) | CURRENT<br>CONSUMPTION (mA) | DIFFERENTIAL<br>SWING (Vp-p) |

|---------------------------|----------------|-----------------------------------|-----------------------------|------------------------------|

| 38.8815                   | 49.97          | 700                               | 18.18                       | 0.593                        |

| 103.68                    | 50.18          | 620                               | 18.26                       | 0.586                        |

| 113.107                   | 50.46          | 600                               | 18.26                       | 0.593                        |

| 124.414                   | 50.21          | 610                               | 18.26                       | 0.606                        |

| 138.241                   | 50.52          | 580                               | 18.26                       | 0.61                         |

| 155.52                    | 50.26          | 600                               | 18.26                       | 0.6                          |

| 177.737                   | 50.81          | 610                               | 18.26                       | 0.598                        |

| 207.363                   | 50.52          | 600                               | 18.25                       | 0.623                        |

| 248.832                   | 50.8           | 450                               | 18.25                       | 0.575                        |

| 311.05                    | 50.62          | 580                               | 18.26                       | 0.547                        |

| 414.733                   | 49.57          | 250                               | 18.27                       | 0.431                        |

| 622.108                   | 50.9           | 220                               | 18.24                       | 0.378                        |

LVDS Output Common-Mode Voltage = 1.27V

LVDS Current Consumption

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NC2008 Data Sheet: TM134 Page 9 Rev: 03 Date: 01/05/2021

Specifications subject to change without notification. See 9co's website for latest revision. © Copyright 2023 9co Not intended for life support applications.

# NC2008 Register Table

| ADDR         | NAME                           | TYPE       | BITS           | DEFAULT   | DESCRIPTION                                                       |

|--------------|--------------------------------|------------|----------------|-----------|-------------------------------------------------------------------|

| 0x00         | Chip ID                        | RO         | 15 - 0         | 0x2008    | Chip ID, it reflects the current product ID,                      |

| ~            |                                |            |                |           |                                                                   |

| 0x01         | Ohin Davisian                  | <b>D</b> O | 7 0            | 0         | Ohio Devision                                                     |

| 0x02         | Chip Revision                  | R0<br>R0   | 7 - 0<br>7 - 0 | 2         | Chip Revision<br>Chip Sub revision                                |

| 0x03<br>0x04 | Chip Sub-Revision<br>XPLL Mode | RW         | 2 - 0          | 0         | XPLL Mode                                                         |

| 0X04         | AFLL WOUG                      | nw         | 2-0            | 0         | 0, 3: power down                                                  |

|              |                                |            |                |           | 1: single-end clk                                                 |

|              |                                |            |                |           | 2: differential clk                                               |

| 0x05         | YPLL Mode                      | RW         | 0              | 0         | YPLL Mode                                                         |

|              |                                |            |                |           | 0: power down                                                     |

|              |                                |            |                |           | 1: power up                                                       |

| 0x10         | XPLL Pre                       | RW         | 2 - 0          | 0         | XPLL pre divider value                                            |

|              | Divider Value                  |            |                |           |                                                                   |

| 0x11         | XPLL FB                        | RW         | 6 - 0          | 0         | XPLL feedback divider value                                       |

| 0.10         | Divider Value                  | DW         |                |           |                                                                   |

| 0x12         | XPLL KVCO                      | RW         | 0              | 0         | XPLL kvco                                                         |

|              |                                |            |                |           | 0: small<br>1: large                                              |

| 0x13         | XPLL CO Value                  | RW         | 0              | 0         | XPLL C0 value                                                     |

| 0/13         |                                | 1100       | 0              | 0         | 0: 100 pF                                                         |

|              |                                |            |                |           | 1: 200 pF                                                         |

| 0x14         | XPLL R0 Value                  | RW         | 3 - 0          | 0         | XPLL R0 Value                                                     |

|              |                                |            |                |           | 0: 3k, 1: 4.2k, 2: 6k, 3: 8.4k, 4:12k, 5: 16.8k, 6: 12k, 7: 16.8k |

|              |                                |            |                |           | 8: 24k, 9: 33.6k, 10: 24k, 11: 33.6k , 12: 46.3k, 13: 66k,        |

|              |                                |            |                |           | 14: 46.3k, 15: 66k                                                |

| 0x15         | XPLL Charge                    | RW         | 10 - 0         | 100       | XPLL charge pump current value,                                   |

| ~            | Pump Current                   |            |                |           | 1.25uA x reg_value                                                |

| 0x16         |                                |            |                |           |                                                                   |

| 0x20         | YPLL2 Pre                      | RW         | 2 - 0          | 0         | YPLL2 pre divider value                                           |

| 0x21         | Divider Value<br>YPLL2 FB      | RW         | 6 - 0          | 0         | YPLL2 feedback divider value                                      |

| UXZI         | Divider Value                  | nw         | 0-0            | 0         |                                                                   |

| 0x22         | YPLL2 KVC0                     | RW         | 0              | 0         | YPLL2 kvco                                                        |

| ONEL         |                                |            | Ũ              | Ŭ         | 0: small                                                          |

|              |                                |            |                |           | 1: large                                                          |

| 0x23         | YPLL2 C0 Value                 | RW         | 0              | 0         | YPLL2 CO value                                                    |

|              |                                |            |                |           | 0: 100 pF                                                         |

|              |                                |            |                |           | 1: 200 pF                                                         |

| 0x24         | YPLL2 R0 Value                 | RW         | 3 - 0          | 0         | YPLL2 R0 Value                                                    |

|              |                                |            |                |           | 0: 3k, 1: 4.2k, 2: 6k, 3: 8.4k, 4:12k, 5: 16.8k, 6: 12k, 7: 16.8k |

|              |                                |            |                |           | 8: 24k, 9: 33.6k, 10: 24k, 11: 33.6k, 12: 46.3k, 13: 66k,         |

| 0x25         | YPLL2 Charge                   | RW         | 10 - 0         | 100       | 14: 46.3k, 15: 66k<br>YPLL2 charge pump current value,            |

| 0x25<br>~    | Pump Current                   | ٩٧ח        | 10-0           | 100       | 1.25uA x reg_value                                                |

| ~<br>0x26    |                                |            |                |           | 1.200M X TEY_Value                                                |

| 0x20         | Output1                        | RW         | 4 - 0          |           | Output1 transmitter mode,                                         |

| 0.01         | Transmitter                    |            | 1 0            |           | Bit[2:0]                                                          |

|              | Mode                           |            |                |           | 0, 6, 7: power down,                                              |

|              |                                |            |                | 1: LVDS   |                                                                   |

|              |                                |            |                | 2: LVPECL |                                                                   |

|              |                                |            |                |           | 3: LVCMOS, P on, N off                                            |

|              |                                |            |                |           | 4: LVCMOS, P off, N on                                            |

|              |                                |            |                |           | 5: LVCMOS, P on, N on                                             |

|              |                                |            |                |           | When transmitter in LVCMOS mode,                                  |

|              |                                |            |                |           | Bit[5:4] control polarity of output                               |

|              |                                |            |                |           | Bit4 0: P is not inverse, 1: P inverse                            |

|              |                                |            |                |           | Bit5 0: N is not inverse, 1: N is inverse                         |

## NC2008 Register Table continued

| ADDR              | NAME                          | TYPE | BITS   | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------|------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x32              | Output2<br>Transmitter Mode   | RW   | 4 - 0  | 0       | Same as Output1 Transmitter Mode                                                                                                                                                                                                                                                                        |

| 0x33              | Output3<br>Transmitter Mode   | RW   | 4 - 0  | 0       | Same as Output1 Transmitter Mode                                                                                                                                                                                                                                                                        |

| 0x34              | Output4<br>Transmitter Mode   | RW   | 4 - 0  | 0       | Same as Output1 Transmitter Mode                                                                                                                                                                                                                                                                        |

| 0x35              | Output5<br>Transmitter Mode   | RW   | 4 - 0  | 0       | Same as Output1                                                                                                                                                                                                                                                                                         |

| 0x36              | Output6<br>Transmitter Mode   | RW   | 4 - 0  | 0       | Same as Output1 Transmitter Mode                                                                                                                                                                                                                                                                        |

| 0x37              | Output7<br>Transmitter Mode   | RW   | 4 - 0  | 0       | Same as Output1 Transmitter Mode                                                                                                                                                                                                                                                                        |

| 0x38              | Output8<br>Transmitter Mode   | RW   | 4 - 0  | 0       | Same as Output1 Transmitter Mode                                                                                                                                                                                                                                                                        |

| 0x39              | XPLL<br>Output<br>Source      | RW   | 0      | 1       | XPLL output source<br>0: Bypass<br>1: XPLL                                                                                                                                                                                                                                                              |

| 0x3a              | YPLL<br>Output<br>Source      | RW   | 0      | 1       | YPLL output source<br>0: Bypass<br>1: YPLL                                                                                                                                                                                                                                                              |

| 0x3b              | Output<br>Source<br>Selection | RW   | 2 - 0  | 0       | Output 1 ~ 8 source selection, output can come from either xpllor ypll, the arrangement are as follows, $0,5,6,7: xpll -> 1,2,3,4,5,6,7,8$ $1: xpll -> 1,2,3,4,5,6$ $2: xpll -> 1,2,3,4,5,6$ $2: xpll -> 1,2,3,4$ $ypll -> 5,6,7,8$ $3: xpll -> 1,2$ $ypll -> 3,4,5,6,7,8$ $4: ypll -> 1,2,3,4,5,6,7,8$ |

| 0x40<br>~<br>0x42 | Output 1<br>Divider<br>Value  | RW   | 19 - 0 | 0       | 20 bit OUTPUT1 divider value                                                                                                                                                                                                                                                                            |

| 0x43<br>~<br>0x45 | Output2<br>Divider<br>Value   |      | RW     | 19 - 0  | 0 20 bit OUTPUT2 divider value                                                                                                                                                                                                                                                                          |

| 0x46<br>~<br>0x48 | Output3<br>Divider<br>Value   | RW   | 19 - 0 | 0       | 20 bit OUTPUT3 divider value                                                                                                                                                                                                                                                                            |

| 0x49<br>~<br>0x4b | Output4<br>Divider<br>Value   | RW   | 19 - 0 | 0       | 20 bit OUTPUT4 divider value                                                                                                                                                                                                                                                                            |

| 0x4c<br>~<br>0x4e | Output5<br>Divider<br>Value   | RW   | 19 - 0 | 0       | 20 bit OUTPUT5 divider value                                                                                                                                                                                                                                                                            |

| 0x4f<br>~<br>0x51 | Output6<br>Divider<br>Value   | RW   | 19 - 0 | 0       | 20 bit OUTPUT6 divider value                                                                                                                                                                                                                                                                            |

| 0x52<br>~<br>0x54 | Output7<br>Divider<br>Value   | RW   | 19 - 0 | 0       | 20 bit OUTPUT7 divider value                                                                                                                                                                                                                                                                            |

| 0x55<br>~<br>0x57 | Output8<br>Divider<br>Value   | RW   | 19 - 0 | 0       | 20 bit OUTPUT8 divider value                                                                                                                                                                                                                                                                            |

NC2008 Data Sheet: TM134 Page 11 Rev: 03 Date: 01/05/2021

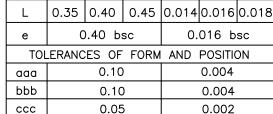

## **Package Outline**

NC2008 Data Sheet: TM134 Page 12 Rev: 03 Date: 01/05/2021

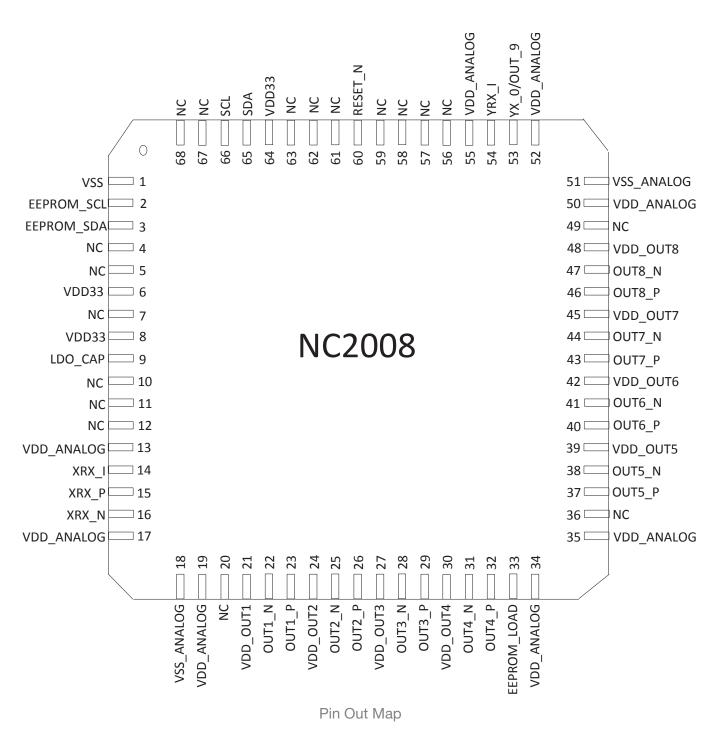

## NC2008 Pin Assignments

| 1      VSS      Power      Digital Ground        2      EEPROM.SOL      1      Serial Data from external EEPROM load        3      EEPROM.SDA      I/O      Serial Data from external EEPROM load        4      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin # | Pin Name   | I/O   | Description                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------|--------------------------------------------------------|

| 3      EEPROM SDA      I/O      Serial Data from external EEPROM load        4      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1     | VSS        | Power | Digital Ground                                         |

| 4      NC      Form        5      NC      9        6      VDD33      Power      3.3V analog power input        7      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2     | EEPROM_SCL |       | Serial Clock Input from external EEPROM load           |

| S      NC      Image: constraint of the state of | 3     | EEPROM_SDA | I/O   | Serial Data from external EEPROM load                  |

| 6      VDD33      Power      3.3V analog power input        7      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4     | NC         |       |                                                        |

| 7  NC  3.3V analog power input    9  LDO_CAP  Connect internal LDO to output capacitor    10  NC  Connect internal LDO to output capacitor    11  NC  Connect internal LDO to output capacitor    12  NC  Connect internal LDO to output capacitor    13  NC  Connect internal LDO to output capacitor    14  XRX,1  I  Accept XO or 3.3V LVPECL/LVDS positive clock output    15  XRX,P  I  Accept XO or 3.3V LVPECL/LVDS negative clock output    16  XRX,N  I  Accept XO or 3.3V LVPECL/LVDS negative clock output    17  VDD ANALOG  Power  Ast analog grower input    20  NC  Control  Stanalog power input    21  VDD, ANALOG  Power  3.3V analog power input    22  OUT1  Power  3.3V analog power input    22  OUT1  Power  3.3V analog power input    23  Out1 P  Differential output 1 nositive (LVPECL/LVDS) or LVCMOS    24  VDD, OUT2  3.3V analog power input    25  OUT2 N  O  Differential output 2 positive (LVPECL/LVDS) or LVCMOS    26  OUT3 N  O  Differential output 3 positive (LVPECL/LVDS) or LVCMOS    29  OUT3 P <t< td=""><td>5</td><td>NC</td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5     | NC         |       |                                                        |

| 8      VDD33      Power      3.3V analog power input        9      LDO CAP      Connect internal LDO to output capacitor        10      NC      Connect internal LDO to output capacitor        11      NC      Image: Stress of the stres of the stress of the stress of the stres of the stres                                                                                                                                                                           | 6     | VDD33      | Power | 3.3V analog power input                                |

| 9      LDO_CAP      Connect internal LDO to output capacitor        10      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7     | NC         |       |                                                        |

| 9      LDO_CAP      Connect internal LDO to output capacitor        10      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8     | VDD33      | Power | 3.3V analog power input                                |

| 10      NC        11      NC        12      NC        13      NC        14      XRX_1      I        Accept XO or 3.3V LVPECL/LVDS positive clock output        15      XRX_P        16      XRX_N        17      VDD_ANALOG        18      VSS_ANALOG        19      VDD_ANALOG        20      NC        21      VDD_OUT1        22      OUT1 N        23      Out1 P        24      VDD_OUT2        3.3V analog power input        25      OUT2 N        26      NC        27      VDD_OUT2        3.3V analog power input        28      OUT2 N        29      OUT2 NO        26      OUT2 NO        27      VDD_OUT3        28      OUT3 NO        29      OUT3 POwer        3.3V analog power input        28      OUT4 NO        29      OUT3 NO        20      Differential output 2 negative (LVPECL/LVDS) or LVCMOS <t< td=""><td>9</td><td>LDO_CAP</td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9     | LDO_CAP    |       |                                                        |

| 12      NC        13      NC        14      XRX.1      I      Accepts single ended clock 3.3V LVCMOS clock output        15      XRX.P      I      Accept XO or 3.3V LVPECL/LVDS positive clock output        16      XRX,N      I      Accept XO or 3.3V LVPECL/LVDS negative clock output        17      VDD.ANALOG      Power      3.3V analog power input        18      VSS_ANALOG      Power      3.3V analog power input        20      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10    |            |       |                                                        |

| 12      NC        13      NC        14      XRX.1      I      Accepts single ended clock 3.3V LVCMOS clock output        15      XRX.P      I      Accept XO or 3.3V LVPECL/LVDS positive clock output        16      XRX,N      I      Accept XO or 3.3V LVPECL/LVDS negative clock output        17      VDD_ANALOG      Power      3.3V analog power input        18      VSS_ANALOG      Power      3.3V analog power input        20      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11    | NC         |       |                                                        |

| 13      NC        14      XRX,1      I      Accept single ended. clock 3.3V LVCMOS clock output        15      XRX,P      I      Accept XO or 3.3V LVPECL/LVDS positive clock output        16      XRX,N      I      Accept XO or 3.3V LVPECL/LVDS negative clock output        17      VDD_ANALOG      Power      3.3V analog power input        18      VSS_ANALOG      Power      3.3V analog power input        20      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |            |       |                                                        |

| 14      XRX_1      I      Accepts single ended clock 3.3V LVPCOL/LVDS positive clock output        15      XRX_P      I      Accept XO or 3.3V LVPECL/LVDS positive clock output        16      XRX_N      I      Accept XO or 3.3V LVPECL/LVDS positive clock output        17      VDD_ANALOG      Power      3.3V analog power input        18      VSS_ANALOG      Power      Analog power input        20      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |            |       |                                                        |

| 15    XRX, P    1    Accept XO or 3.3V LVPECL/LVDS positive clock output      16    XRX, N    1    Accept XO or 3.3V LVPECL/LVDS negative clock output      17    VDD_ANALOG    Power    3.3V analog power input      18    VSS ANALOG    Power    Analog Ground      19    VDD_ANALOG    Power    3.3V analog power input      20    NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |            |       | Accepts single ended clock 3.3V LVCMOS clock output    |

| 16      XRX_N      I      Accept XO or 3.3V LVPECL/LVDS negative clock output        17      VDD_ANALOG      Power      3.3V analog power input        18      VSS_ANALOG      Power      Analog Ground        19      VDD_ANALOG      Power      3.3V analog power input        20      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |            |       |                                                        |

| 17    VDD_ANALOG    Power    3.3V analog power input      18    VSS_ANALOG    Power    Analog Ground      19    VDD_ANALOG    Power    3.3V analog power input      20    NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |            |       |                                                        |

| 18      VSS_ANALOG      Power      Analog Ground        19      VDD_ANALOG      Power      3.3V analog power input        20      NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |            | Power |                                                        |

| 19    VDD_ANALOG    Power    3.3V analog power input      20    NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18    |            |       |                                                        |