#### **Overview**

The NS2000-1PPS is a highly integrated time and frequency synchronizing ASIC. This design implementation is dedicated for use in applications which specifically require locking to an incoming 1PPS reference signal. This high precision phase and frequency synchronization solution also integrates low noise frequency generation and/or frequency translation. This product can be used to support a high-stability frequency reference for use in wireless systems, IEEE 1588v2, and applications employing a 1PPS frequency source for high precision, long term time and frequency generation.

The NS2000-1PPS allows the user access to the chip's internal phase detector to calibrate and correct for saw tooth error typically found on a 1PPS signal emanating from a GNSS receiver. Another feature provides the user access to the internal master clock and NCC

a GNSS receiver. Another feature provides the user access to the internal master clock and NCO which can be used to calibrate and correct for drift found in the external supporting OCXO or TCXO. With less than 1 ppt resolution, the user may compensate in holdover mode for frequency instabilities due to temperature change or long term aging characteristics.

An external precision OCXO or TCXO provides the system's master clock for various holdover performance options as well as the support for multiple filter bandwidth options from <1mHz to .05 Hz. Up to two external disciplined VCXOs provide the output characteristics for phase noise and jitter performance for any combination of 10 differential or 21 single ended clock outputs with output jitter performance options of sub100fs RMS (12kHz to 20MHz).

## Features

- Accepts 1 PPS Reference input

- Programmable phase alignment of outputs to 1 PPS reference input

- Internal NCO for SAW tooth error smoothing

- Locked, HO, & Free-run indication. Holdover options available to .001ppb resolution

- 1Hz to 800 MHz clock output frequency range

- Ten differential or up to 23 single ended Low Jitter Clock Outputs

- Programmable output transmitters (programmable as either 1 LVPECL, 1 LVDS or 2x LVCMOS output)

- Low jitter clock outputs (less than .3ps RMS (12kHz to 20MHz) with options for sub 100fs)

- Programmable bandwidth settings for multiple applications

- I2C Interface for system communication and interrogation.

- 3.3VDC Supply Voltage

- -40C to +85C operating temperature range

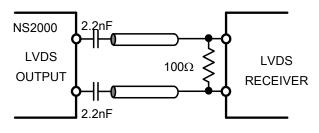

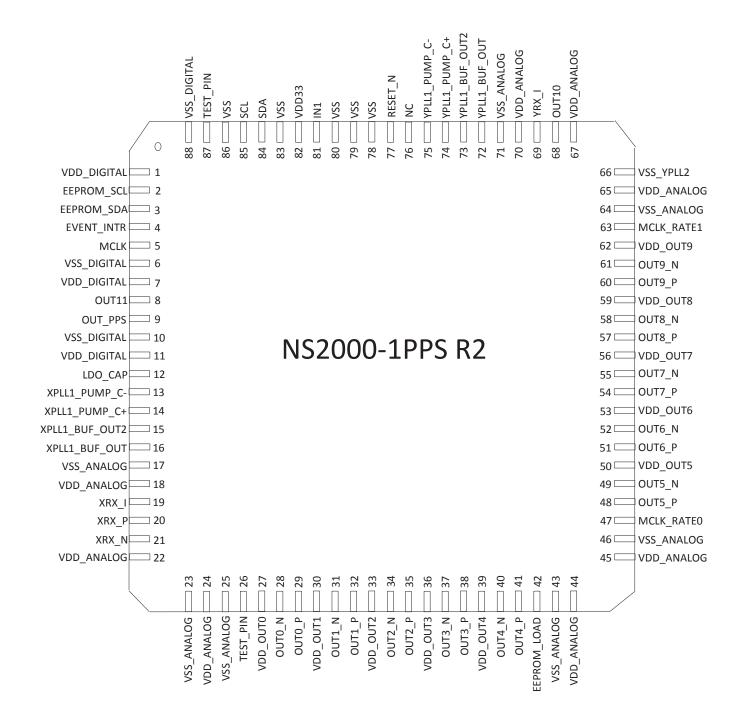

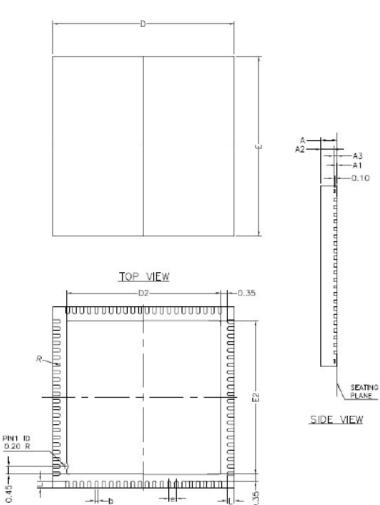

- 10 x10 mm 88 pin QFN surface mount package

# Applications

- Primary Reference Time Clock (PRTC) [G.8272]

- Telecom Grand Master [G.8273.1]

- Telecom boundary clock [G.8273.2]

- Wireless Base Stations

- GNSS Disciplined Oscillator

- NTP Stratum 0 Standard

| Bulletin | TM139       |

|----------|-------------|

| Revision | 10          |

| Date     | 31 May 2022 |

S H E T

Δ

Delivering a New Generation of Time and Frequency Solutions for a Connected World.

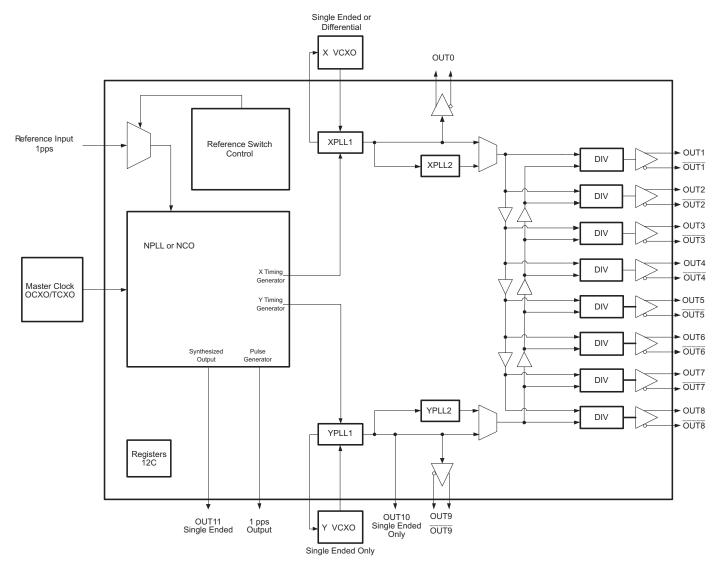

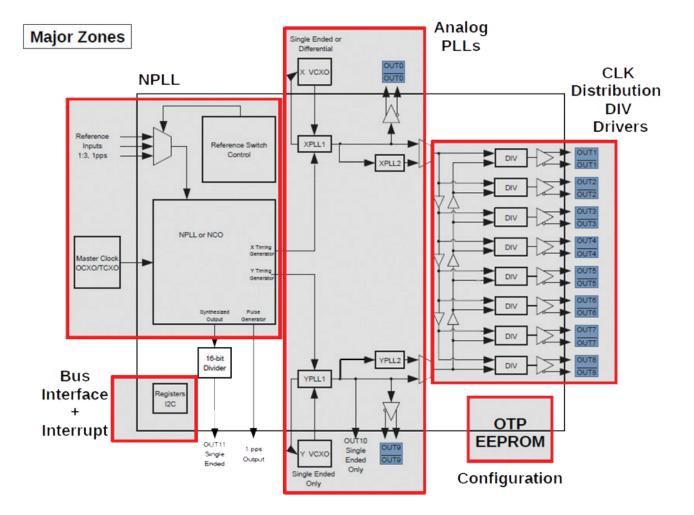

# NS2000-1PPS Functional Block Diagram

## NS2000-1PPS Specifications

| Parameter                         | Specification                                          |

|-----------------------------------|--------------------------------------------------------|

| Voltage                           | 3.3V ±5%                                               |

| Power                             | Based on configuration (300mA with outputs tri-stated) |

|                                   | Outputs add: LVPECL 50mA, LVDS 20mA, LVCMOS 8mA        |

| Temperature                       | -40 to 85°C Industrial temp range operation            |

| Reference Frequency (1PPS)        | 1 Pulse Per Second (1Hz) 3.3 V DC ref                  |

| Low Jitter Clock Output Frequency | 1Hz to 800 MHz                                         |

| DPLL Synthesized Output Frequency | 10MHz to 80MHz plus 1 PPS                              |

| Holdover stability                | 0.001 ppb capable                                      |

| Dimensions                        | 10 x 10 x 1mm 88 pin QFN package                       |

# **General Description**

The NS2000-1PPS is a highly integrated PLL time and frequency synchronizing integrated circuit that receives a single 1PPS reference input and generates multiple outputs locked to the rising edge of the 1PPS pulse. The 1PPS reference can be generated from a GNSS source. The chip is capable of correcting for the 1PPS signal's quantization error effectively reducing the saw tooth error typically found on GNSS receiver generated 1PPS signals.

The design architecture incorporates a sophisticated digital and analog PLL scheme to provide up to 23 phase/frequency locked clock outputs at frequencies from 1.5 kHz to 800 MHz including a 1PPS pulse generator output. The system is clocked with an external precision OCXO or TCXO providing the basis for various holdover and free run performance options. A variable bandwidth filter (0.35 mHz to .05 Hz) enables supporting phase locking to high jitter 1 PPS input references to less than 1ns resolution. The phase relationship between the 1PPS input reference and output ports can be controlled with programmable settings.

The chip digitally synthesizes up to four independent frequencies from the timing generator. Two outputs are brought out directly from the NPLL synthesizer (including the 1PPS pulse generator) and another two outputs function as reference inputs to the two analog PLL chains within the chip. These two signals can be attenuated internally to ultra low jitter levels and provide the source for multiple output clocks in the chip's clock distribution section.

The analog portion of the chip consists of two independent PLL chains (X side and Y side) that attenuate jitter through a variety of optional configurations to achieve the user's desired performance level. The chip can operate with either X side or Y side analog PLLs or outputs can be generated from a combination of both X and Y side. One or two disciplined VCXO(s) provides the output characteristics for phase noise and jitter performance for up to 21 clock outputs (10 differential or 21 single ended) with optional configurations that can provide output jitter performance of less than 100fs RMS over the integration range of 12 kHz to 20MHz. The 1 PPS pulse generator is independently controlled and a 1PPS pulse can be generated in holdover mode.

Delivering a New Generation of Time and Frequency Solutions for a Connected World.

NS2000-I Data Sheet: TM139 Page 3 Rev: 10 Date: 05/31/2022

## Internal NPLL and Numeric Timing Generator

The kernel of the NS2000-1PPS is a digital-based numerical PLL. In its core, all internal modules are either digital or numerical, including the phase detectors, filters, timing generator and clock synthesizers. The pure digital design timing generator allows the NS2000-1PPS to become an accurate and reliable deterministic system.

The NS2000-1PPS includes a single timing generator. This timing generator can individually operate in free run, synchronized, and holdover mode. The timing generator must be placed in either external-timing mode or self-timing mode via register settings. External timing mode supports "synchronized" mode. In external timing mode, the systems NPLL phase locks to the 1 PPS external reference input. In "synchronized" mode, the NS2000-1PPS's PLL loop bandwidth may be programmed from <1mHz to .05 Hz to vary the timing generator's filtering function.

Self-timing mode supports "free run" and "holdover" modes. In self-timing mode, the PLL simply tunes the clock synthesizers to a given fractional frequency offset. When the 1PPS reference input and previous holdover history are unavailable, such as in system's initialization stage, free-run mode will be entered and used. When the selected reference input is unavailable but a long-term holdover history accumulated in previous synchronized mode is available, holdover mode may be entered or used. In NS2000-1PPS, the free-run clock is derived from the MCLK (external oscillator) and digitally calibrated to compensate the external oscillator's accuracy offset.

Three internal clock synthesizers generate output signals at any frequency (divisible by 8 kHz) from the systems timing generator. Two of these outputs are used internally as reference inputs to the X and Y side analog PLL chain. The output frequency of the synthesizers which support the X and Y side analog PLL chains are register programmable to any frequency divisible by 8 kHz.(8 kHz \* M where 1 < M <=5000). The third generates a 1PPS pulse. These synthesized clocks are phase and frequency locked to the internal NPLL.

The system timing generator is supported by an internal numerically controlled oscillator (NCO) that is timed by the systems master clock. The NS2000-1PPS reports to the user the frequency offset between that of the system master clock and that of the incoming reference in "Locked" mode. When in "holdover" mode, the NCO's frequency offset can be externally controlled via registers in the chip to calibrate the master clock. This functionality allows the user to externally compensate the NCO output to address drift from temperature fluctuations and/or long term drift characteristics of the external OCXO or TCXO. The NCO offset control has a resolution of less than 1 part per trillion.

# Master Clock (MCLK) and Programmable Bandwidth Settings

The system's master clock (MCLK) requires a "fixed" frequency clock input and is used to clock the NS2000-1PPS NPLL. The NS2000-1PPS can be configured to accommodate one of two master clock frequencies – 10MHz or 20 MHz via state settings on pins 36 and 49.

The master clock's performance characteristics should be consistent with chosen bandwidth settings and desired holdover and free run performance requirements. Bandwidth setting options are programmable in the NS2000-1PPS from .35 mHz to approximately .05 Hz. When locking to a high jitter 1PPS input signal, a low bandwidth filtering algorithm should be employed using a bandwidth setting in the NS2000-1PPS below 1mHz. For optimal performance when using low bandwidth settings, the short term stability level of the master clock should be consistent with the Stratum 3E performance requirement. Using a bandwidth setting of .35 mHz and an appropriate master clock, the 20ns jitter from a typical 1PPS GNSS source can be reduced into the range of <1ns. Higher bandwidth settings like .05Hz, can be supported by a TCXO with the appropriate short term stability specification. A variety of master clock options are available from Connor-Winfield to support the NS2000-1PPS .

The desired frequency input choice is hardware controlled and can be configured by setting the appropriate pins (Pin 36 and Pin 49) to the specific logic level as shown in the table below.

| MCLK Frequency Desired | Pin 49 MCLK_Rate 1 | Pin 36 MCLK_Rate 0 |  |

|------------------------|--------------------|--------------------|--|

| 10.0 MHz               | 0                  | 0                  |  |

| 20.0 MHz               | 0                  | 1                  |  |

Table 1 Master Clock Frequency Selection list

#### Inputs IN1, IN2, IN3

The NS2000-1PPS has three input ports IN1, IN2 and IN3. However only one port can be chosen at a time to be used as the input to the DPLL. In the 0x35 NPLL\_START register, a value is required to start the NPLL. The value chosen determines which input port the 1PPS incoming signal will be arriving on.

## **Phase Synchronization General**

The NS2000-1PPS digital core generates a synchronized clock, used as the frequency input source for an internal analog, clean up PLL. The synthesized clock output can be programmed to any frequency divisible by 8 kHz to support phase / frequency matching in the downstream analog clean up APLL portion of the IC. In synchronized mode, the phase relationship between the selected reference input and the clock output may be phase arbitrary or frame phase aligned. A zero frame phase relationship is produced by programming in frame phase align mode. An additional synthesized and phase aligned output is the 1 PPS pulse generator.

## **1PPS Locking and Phase Synchronization Solution**

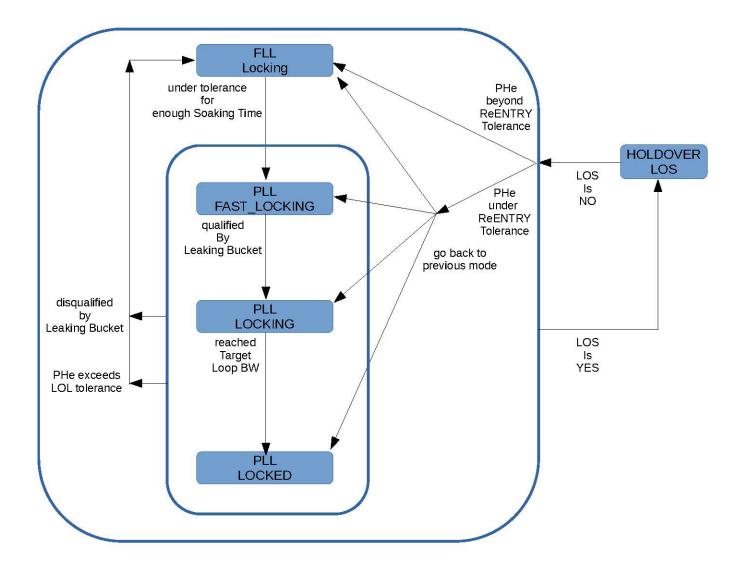

The NS2000-1PPS phase locking design implementation employs a low bandwidth filtering scheme with multiple locking stages during the complete phase locking process.

Register NPLL\_MODE 0x20 provides status of the various locking stages. In addition, this register reports when the fast locking phase is complete and the NPLL is locked to the incoming 1PPS signal and when the phase bias has been eliminated between the phase alignment frequency chosen and the incoming 1PPS signal.

## General Theory of Operation: 1PPS Locking and Phase Synchronization Solution

When the NPLL is "kicked up", the IC starts to operate in IDLE\_LOS mode. All the clock/pulse outputs are disciplined by or generated from the external MCLK source, at its initial frequency accuracy, or in conjunction with any user specified frequency offset calibration instructions set in register 0x4F. When the IC detects a valid 1PPS input, it first calculates the real phase position of those input pulses, adjusting for any user specified phase detector calibration setting in register 0x4D, and then measured every period of this 1PPS input.

The NPLL then moves to operate in FLL\_LOCKING mode. In this operation mode, the IC adjusts its clock/pulse output frequency attempting to "frequency lock" to the 1PPS input. The user can specify a "soak" time to allow the system to settle. During this soak time, the phase error between the incoming 1PPS and the output 1PPS is measured internally. Cycles where the phase error between the two 1PPS pulses increases, adds to a leaking bucket value. Cycles where the phase error between the two 1PPS pulses decreases, subtracts from the value of a leaking bucket. If the leaking bucket incrementally fills to the threshold level, the soak time counter will reset and begin the FLL process again. If the value of the leaking bucket incrementally reduces to zero level, this indicates that the system has settled down to become frequency locked. At this point, the operation then moves from the frequency locking (FLL) stage to phase locking stage (PLL), starting with a fast locking (PLL\_FAST\_LOCKING) phase.

The PLL first operates in the PLL\_FAST\_LOCKING mode, where typically a higher bandwidth value is chosen relative to a "target" or final bandwidth setting at which the NPLL is set to permanently operate at. In the beginning of this stage, a large phase offset can exist between the 1PPS input and IC's 1PPS output even after the frequency lock loop settles down. In the next 1PPS output, it will jump from its original projected phase position to whatever nearest phase position is estimated to be on the next 1PPS input. The 1PPS output can be controlled through registers so as not to immediately jump to the exact estimated phase position automatically in case the user requests, through register settings, to maintain its phase alignment with some other clock output. The phase difference can be built out over a period of time to avoid introducing an immediate phase hit to the PLL. This PBO (phase build-out) will then be compensated back to the clock/pulse outputs slowly and smoothly out of band without impacting the PLL.

When operating in the FLL and PLL locking modes, the IC employs a "leaking bucket" mechanism which is used to evaluate the phase synchronization condition of the PLL. This condition can be monitored through the registers. The leaking bucket starts at one half of its set value. Based on internal measurements of phase error, the bucket either adds or subtracts a numerical count when each pulse is measured. If the phase error between the incoming 1PPS signal and the 1PPS output increases, it adds one 1 each corresponding second. If the phase error decreases between the input and output 1PPS signal, the bucket value is reduced by one for that pulse. When the bucket is filled beyond the level of its assigned capacity, the system will revert back to the previous locking mode and begin the process again. The leaking bucket threshold level is identified in nS and size of the leaking bucket is an integer number associated with length of time (accumulated 1PPS pulse periods) the user desires to observe prior to allowing the system to the next locking stage.

These design factors are important to consider, based on the bandwidth level chosen and the master clock source. If using an OCXO as the master clock source, an OCXO may take a long time to warm up and settle. When the leaking bucket level is reduced to "0", indicating the evaluation result is good, the operation mode automatically will move from the fast locking stage to PLL locking stage.

In PLL\_LOCKING mode, the "target" PLL loop bandwidth is typically set to a lower loop bandwidth than used in the FAST\_LOCKING mode. Based on a user register value specified rate, the system smartly adjusts its PLL loop BW to approach user's end bandwidth target value. Once the target PLL loop BW is reached and the leaking bucket indicates the result is good, the operation will be labeled as being in PLL\_LOCKED mode.

For any reason either if PLL's leaking bucket mechanism claims a bad phase synchronization evaluation result or if the phase error between the calibrated 1PPS input and the 1PPS output exceeds the user specified loss of lock (LOL) tolerance, the operation mode will be pushed back to FLL\_LOCKING mode.

In the case where the 1PPS input signal is lost due to cable disconnection, signal glitches, manually forcing into holdover or any other reason, the operation will be pushed back to the IDLE\_LOS mode. The NPLL will work as a holdover clock generator internally, derived solely from the master clock (MCLK) in conjunction with the user's frequency calibration instructions, if any. When a good quality (valid) 1PPS input signal returns and is present, the phase error between the calibrated 1PPS input and the current 1PPS output will be used determine whether the operation mode should resume to its mode prior to this LOS condition or go to FLL\_LOCKING mode directly based on the user defined re-entry phaser error tolerance setting (PHe\_REENTRY\_TOLERANCE) in the registers.

# General Theory of Operation: 1PPS Locking and Phase Synchronization Solution continued

#### PBO and its Compensation

As illustrated previous, a phase built-out may be executed when moving operation from FLL\_LOCKING mode to PLL\_FAST\_LOCKING mode. This phase offset will be compensated back to all the clock/pulse outputs smoothly. Users can specify the maximum limit of the additional frequency offset being applied to all the clock/pulse outputs in order to compensate those phase offset back. The frequency offset acceleration rate is decided by the max allowed additional frequency offset.

$\label{eq:frequency} frequency offset \ acceleration = \frac{max \ allowed \ frequency \ offset}{16.384 \ sec}, \ no \ less \ than \ 1 \ ppb \ / \ sec$

The phase shifting to compensate back the PBO phase offset will be smooth. The frequency offset will be speed up in the beginning and stay at its maximum offset if the limit was met. When approaching to its phase offset destination, it will slow down to finally stop at the phase position it targeted. Once all the PBO phase offset being compensated has completed, the PBO compensation "done" status will be claimed. This whole phase shirting process is out-of-band to the PLL, regarding to whatever the PLL's loop bandwidth is.

#### **RUN TIME REGISTERS**

The NS2000-1PPS requires most all NPLL parameters to be set in the registers prior to starting the NPLL using register 0x35 NPLL\_ KICKUP. Once the NPLL is started, no changes to the register settings will be recognized. However, certain registers are identified in the register description as \_RT\_ or "run time" registers. Once the NPLL is "kicked up", only NPLL registers identified as \_RT\_ can be adjusted and recognized by the IC during operation. All non \_RT\_ registers must be set prior to the kick up of the NPLL. Run time registers were designed and intended to allow the user to monitor the performance of the system and dynamically make adjustments within the system to compensate for those conditions. Examples of the run time registers are: NPLL\_RT\_PD\_CALI (phase adjustment for quantization error correction, NPLL\_RT\_MCLK\_CALI (frequency offset correction), NPLL\_RT\_PLL\_LBW\_TARGET (target bandwidth adjustment if locking conditions need real time adjustment).

For all registers requiring setting prior to starting the NPLL, a suggested programming sequence is provided in this document after the register table pages.

#### The PLL Loop Bandwidth of FAST\_LOCKING Mode

The PLL loop bandwidth in FAST\_LOCKING mode is programmable. However, the bandwidth should be set no higher than 100 mHz. If this register is set higher than 100 mHz, the register value will be ignored and this bandwidth will stay as 100 mHz.

#### The Target PLL Loop Bandwidth

The target loop bandwidth is programmable in runtime. This target bandwidth must not be set higher than the bandwidth for FAST\_LOCKING mode. Otherwise, the register value will be ignored and the internal target bandwidth will be set to be same as the bandwidth for FAST\_LOCKING mode.

#### Between LOCKING mode and LOCKED mode

In run time, if the current working PLL bandwidth is no higher than the target bandwidth, the NPLL mode will be promoted from LOCKING to LOCKED. The NPLL mode will be demoted from LOCKED to LOCKING once the target bandwidth is reprogrammed to be lower than the current running bandwidth.

# General Theory of Operation: 1PPS Locking and Phase Synchronization Solution continued

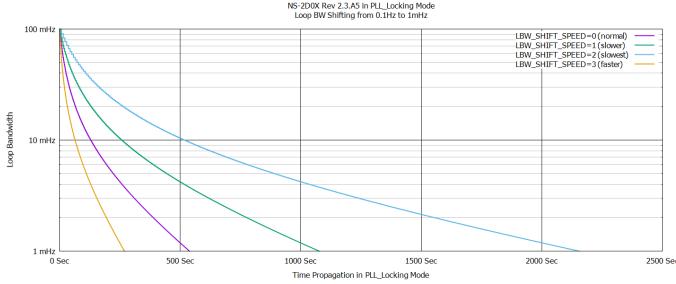

#### LBW Shifting Speed in PLL\_Locking Mode

The loop bandwidth shifting speed can be configured in register NPLL\_CONFIG. While the NPLL is in PLL\_Locking mode, its loop bandwidth will slowly shift into the target normal loop bandwidth at one of four shifting speeds as chosen in register NPLL\_RT\_PLL\_LBW\_TARGET. The bandwidth shifting speed is not linear.

LBW Shifting from 100mHz down to 1mHz

#### PHe Tolerances

The system monitors the difference between the phase eror of the incoming 1PPS signal the the 1 PPS Output signal. The user determines the phase error tolerance level to initiate a loss of lock (LOL) condition using register NPLL\_RT\_Phe\_LOL\_TOLERANCE. The user also determines the re-entry phase error threshold level for avoiding re-starting in FLL\_Locking Mode if the phase error stays within a given range during holdover periods. Register NPLL\_RT\_PHe\_ReENTRY\_TOLERANCE ais used to set this level. Please note that both registers are run-time registers for dynamic runtime control.

#### PLL modes and Leaking Bucket operation

While promoting the operation mode, the loop bandwidth will be switched to the relative loop bandwidth preassigned to that mode. The system uses one leaking bucket to promote from PLL\_FAST\_LOCKING to PLL\_LOCKING and to claim the LOL events. While promoted from PLL\_FAST\_LOCKING to PLL\_LOCKING, the loop bandwidth will migrate from PLL\_FAST\_LOCKING's loop bandwidth to the target loop bandwidth slowly and smoothly following the speed rate user specified. After reaching the "target" normal loop bandwidth, the operation mode moves to PLL\_LOCKED. The exact running PLL loop bandwidth at any moment could be read out from register (NPLL\_PLL\_LBW\_IDX\_NOW).

#### **ReENTRY from Holdover/LOS mode**

The phase error between the 1PPS\_IN and 1PPS\_OUT, will dictate how the system recovers from an LOS or Holdover mode condition. If the measured phase error is beyond the ReENTRY threshold, level set in the registrers, the system will revert to FLL locking mode. Otherwise, the system will go back to the mode prior to entering HOLDOVER mode due to LOS events.

#### From FLL Locking to PLL Locking

The criteria to promote the NPLL mode from FLL locking to PLL locking is to continually have a given quality condition to be satisfied for a certain soaking time. Any condition violation resets the soaking time counter. The mechanism measures the peak-to-peak frequency offset (versus the calibrated MCLK) on the FLL output and must maintain within the given frequency tolerance.

#### The PLL Loop Bandwidth of FAST\_LOCKING Mode

The PLL loop bandwidth in FAST\_LOCKING mode is programmable. However, the bandwidth should be set no higher than 100 mHz. If it was, the register value will be ignored and this bandwidth will stay as 100 mHz.

# General Theory of Operation: 1PPS Locking and Phase Synchronization Solution continued

#### The Target PLL Loop Bandwidth

In run time, if the current working PLL bandwidth is no higher than the target bandwidth, the NPLL mode will be promoted from LOCKING to LOCKED. The NPLL mode will be demoted from LOCKED to LOCKING once the target bandwidth is reprogrammed to be lower than the current running bandwidth.

#### Between LOCKING mode and LOCKED mode

In run time, if the current working PLL bandwidth is set no higher than the target bandwidth, the NPLL mode will be promoted from Phase LOCKING to Phase LOCKED. The NPLL mode will be demoted from LOCKED to LOCKING once the target bandwidth is reprogrammed to be lower than the current running bandwidth.

#### Holdover and Loss of Signal (LOS)

Holdover mode is available after the system has successfully locked to a valid 1PPS reference input signal. There are two ways in which the system can move into holdover mode. Register 0x36 [7:0] NPLL\_RT\_CTRL allows the user to manually force the system into a Loss of Signal (LOS) mode. The other is when the system detects that no signal exists on the incoming reference. This condition will put the system into Holdover mode automatically. Through its internal counter, the NS2000-1PPS can detect the existence of a 1PPS signal, however, it does not perform any qualification evaluation of the validity of the 1PPS signal.

In return from Holdover mode, the NS2000-1PPS design allows the user to set phase error tolerance threshold levels to control the sequence when re-entering the locking process.

#### Phase Detector Calibration/Saw Tooth Error Correction

The NS2000-1PPS provides access to the chip's internal phase detector to enable dynamic adjustment to address and correct for the saw tooth noise and adjust phase offset due to antennae cable runs. In dynamic use, the register value must be ready when its associated 1PPS input pulse arrives. The readiness of this register's value must be compliant to a minimum set time (10uS) and hold time (125 uS). Generally, calibrating quantization error reported by the GNSS receiver is the primary use for this register's functionality.

#### Frequency Offset Calibration

The NS2000-1PPS provides the user an ability to digitally fine tune its internal master clock. The calibration range is  $\sim \pm 114$  ppm. The internal master clock is boosted in frequency from the external clock source used. In holdover mode, this feature can be used to accommodate for predictable drift in the external clock to compensate for changes in frequency due to temperature change or long term drift due to aging. Using an OCXO that has been designed for temperature coefficient correction can be used in conjunction with this feature. This feature provides the user a resolution of < 1 ppt per step. Negative values decreases the frequency. Positive values increases the frequency.

# EVENT\_INTR

The NS2000-1PPS provides an event interrupt notification function (EVENT\_INTR pin 4). This pin's sole function is to notify the user when the NPLL\_MODE status changes.

In this one bit register, the interrupt pin becomes "active" when at least one bit is non-zero. The current interrupt status can be read from this register. Once the interrupt pin is activated, it can only be deactivated when the interrupt status has been erased. The user can write to this register, however, its operation is not "write-the-value- then-replace-the-value". It is a bit-operation. For each bit, write "1" to erase that bit value. It can be stated as: INTR\_STATUS = INTR\_STATUS & (~VALUE).

| ADDR      | BITS   | NAME       | I/0 | DEFAULT | DESCRIPTION     |                              |

|-----------|--------|------------|-----|---------|-----------------|------------------------------|

| 0x07~0x08 | [15:0] | INTR_EVENT | RW  | 0       | Interrupt Event |                              |

|           |        |            |     |         | bit[0]          | REG(NPLL_MODE) value changed |

|           |        |            |     |         | bit[15~1]       | ~ RSVD ~                     |

# **1PPS Output**

The 1PPS output's pulse width can be programmed in the NS2000-1PPS.

| ADDR      | BITS   | NAME             | I/0 | DEFAULT | DESCRIPTION                          |

|-----------|--------|------------------|-----|---------|--------------------------------------|

| 0xA0~0xA1 | [11:0] | 1PPS_PULSE_WIDTH | RW  | 10      | 1PPS output pulse width. Unit in uS. |

# Synthesized Output 11

The NS2000-1PPS provides a programmable LVCMOS 3.3V output that can generate clock frequencies from ~152Hz to 80 MHz. An initial stage at register 0xA7~0xA8 allows the user to generate an 8kHz divisible frequency from 10MHz to 80MHz. Through the use of a 16 bit post divider at register 0xA9~0xAA, frequencies generated in the initial stage can then be further integer divided to a lower frequency by setting a value in the post divider register. However, only frequencies divisible by 8kHz can be phase aligned to the rising edge of the incoming 1PPS signal.

## Phase Alignment to Clock Outputs

The NS2000-1PPS can be configured to phase align the rising edge of incoming 1PPS signal with the rising edge of the frequency outputs generated in the two analog PLL chains, OUT\_11 driven by the synthesized outputs from the NPLL's timing generator, and the rising edge of the 1PPS output. For alignment to occur however, frequencies generated must be integer divisible by 8kHz. A valid frequency must be reported in register 0x46~4B and a valid phase build out rate must be entered into register 0x4C in order for the phase alignment function to successfully operate. If generating multiple outputs at different frequencies, the highest common divided integer frequency among the output frequencies generated should be chosen to be input into the NPLL\_RT\_ALIGNED\_OUT\_FREQ register. Frequencies identified in the NPLL\_RT\_ALIGNED\_OUT\_FREQ register can be chosen as low as 8kHz for purposes of finding a common related frequency. Both or either X and Y side APLL chains can be set to align with the 1PPS signal.

Once the NPLL is started using register NPLL\_START, a phase build out process begins to bring the clock output into phase alignment with the rising edge of the incoming 1PPS signal. A default phase error build out rate can be chosen between 10 pS/S and 2.55 nS/S. When very low frequencies are to be generated, a "wide range" mode can be enabled to increase the speed of the phase build out rate. The build out rate is set in the NPLL\_PHASE\_SHIFT\_SPEED register, depending upon using default or Align-in-Wide-Speed mode.

| ADDR    | BITS   | NAME                     | I/0 | DEFAULT | DESCRIPTION        |                                                      |

|---------|--------|--------------------------|-----|---------|--------------------|------------------------------------------------------|

| 0x45    | [7:0]  | NPLL_CONFIG              | R/W | 0       | NPLL's phase align | configuration                                        |

|         |        |                          |     |         | bit[0]:            | Phase aligned to 1PPS on XPLL: 1=YES, 0=N0           |

|         |        |                          |     |         | bit[1]:            | Phase aligned to 1PPS on YPLL: 1=YES, 0=N0           |

|         |        |                          |     |         | bit[3:2]:          | PLL_LBW_SHIFT_SPEED                                  |

|         |        |                          |     |         |                    | ify the LBW shifting speed in PLL_LOCKING mode       |

|         |        |                          |     |         |                    | W(FAST_LOCKING) to LBW (NORMAL)                      |

|         |        |                          |     |         |                    | 0: normal                                            |

|         |        |                          |     |         |                    | 1: slower                                            |

|         |        |                          |     |         |                    | 2: slowest                                           |

|         |        |                          |     |         |                    | 3: faster                                            |

|         |        |                          |     |         | bit[7:4]:          | ~RSVD~                                               |

| 0x46~4B | [47:0] | NPLL_RT_ALIGNED_OUT_FREQ | R/W | 0       | The frequency of o | utput to align to 1PPS output. 17-bit. Unit in 8kHz. |

|         |        |                          |     |         | bit [16:0]         | n, freq = 8kHz x n                                   |

|         |        |                          |     |         | bit [47:17]        | must be zero                                         |

## NS2000-1PPS Analog PLL Chain General Description

The NS2000-1PPS supports two independent analog PLL chains (X,Y) to support two simultaneous, independent frequency domains that share ten programmable clock output transmitter ports. There is an additional single ended output on the Y-side (Output 10). The NS2000-1PPS consists of two (2) independent sets of two (2) cascaded PLL stages, referred to as the X and the Y side. In each X and Y side of the chip, the first stage PLL (XPLL1 and YPLL1) attenuates the initial jitter from the reference input/NPLL with the use of an external VCXO.

When in operation, the locked VCXO signal can be sent directly to the output transmitter ports for a direct pass through of the VCXO frequency or further divided using the independent 20 bit divider circuits at each output transmitter port.

Alternatively, the VCXO frequency/signal can be sent to a second stage PLL. A second stage PLL for each X and Y side (XPLL2 and YPLL2) with an integrated high frequency VCO is available to accept the output of the first stage PLL1. Each PLL2 has an integrated phase frequency detector, charge pump and VCO in the usable range of 1.2GHz to 1.475 GHz that can be employed to generate locked output clocks at the eight output transmitter ports using the eight independent 20 bit divider circuits found at each transmitter ports.

This design architecture gives the user a great deal of control over the output phase noise and jitter level generated by the NS2000-1PPS . An external VCXO with exceptional phase noise and jitter performance can be used in bypass mode of the NS2000-1PPS to retain the ultra-low jitter performance characteristics with very little additive jitter contributed by the NS2000-1PPS . Low frequency VCXO sources (as low as 1 MHz) as well as differential clock sources (up to 800 MHz) can be used in bypass mode to achieve maximum jitter attenuation. If outputs are generated using PLL2, single ended VCXOs at frequencies between 40 MHz and 100 MHz should be used for best performance. Depending upon the external VCXO configuration used, clock outputs can be generated in the frequency range from 1Hz to 800MHz, limited to 180MHz for LVCMOS outputs.

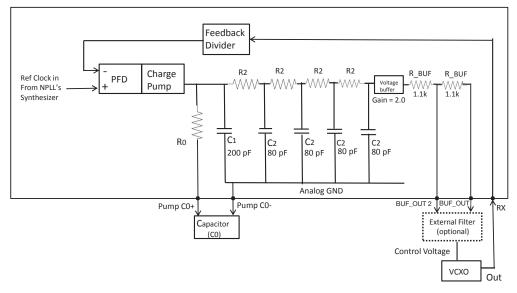

## PLL1 (X,Y) General Description

PLL1's (X,Y) function in the NS2000-1PPS it to act as a frequency translator and jitter attenuator. PLL1(X,Y) effectively attenuates the jitter from the incoming reference clock and translates the frequency to that of the chosen external VCXO which supports it. PLL1(X,Y) can pass through the external VCXO frequency directly to the output dividers and transmitters or be used as the input frequency to the second stage PLL, PLL2 (X,Y). When the VCXO clock output is passed directly through to the output dividers and transmitters, the NS2000-1PPS is capable of attenuating the jitter with approximately 10fs additive jitter to that of the external 3.3V VCXO.

PLL1(X,Y) consists of a phase-frequency detector (PFD), charge pump, passive loop filter, and an external VCXO operating in a closed loop. PLL1(X,Y) has the flexibility to operate with a loop bandwidth of approximately 10Hz to 200 Hz. This relatively narrow loop bandwidth gives it the ability to suppress jitter that appears on the synthesized clock signal feeding PLL1 from the NS2000-1PPS 's NPLL. This synthesized clock eliminates the requirement for a phase detector frequency relationship between the frequency of the reference inputs into the NS2000-1PPS and the output VCXO frequency desired. The NPLL's synthesizer frequencies are programmable allowing for a flexible phase detector rate however the PFD rate must be divisible by 8kHz (8 kHz \* M where <1 M <=5000). The charge pump current ,feedback divider, R0,and R2 are register programmable inside the chip. Capacitors C1 and C2 are internal and are fixed values. One external capacitor is required for the NS2000-1PPS's loop filter, which connects to pins Pump\_C0+ and Pump\_C0-. An optional external filter on the control voltage pin of the external VCXO is supported through BUF\_OUT2 and BUF\_OUT2 is output.

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NS2000-I Data Sheet: TM139 Page 11 Rev: 10 Date: 05/31/2022

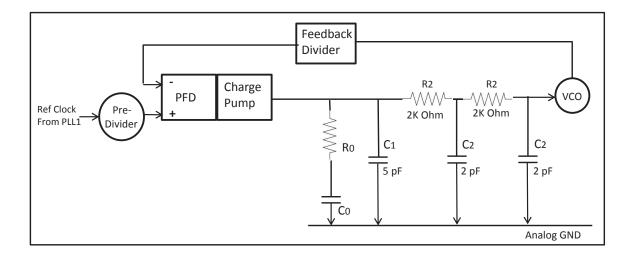

# PLL2 (X, Y) General Description

PLL2(X,Y) operates as a second stage analog PLL block, taking its reference input from PLL1 (X,Y). PLL2 (X,Y) consists of a fully integrated phase-frequency detector (PFD), charge pump, integrated loop filter, and integrated internal VCO operating in a closed loop. The NS2000-1PPS 's internal VCO operates in the frequency range from 2.4GHz to 2.95GHz, however an internal pre-divider ( by 2) makes the effective programmable VCO frequency range available from 1.2GHz to 1.495 GHZ. Through programmable registers, the input frequency from PLL1 (X,Y) can be integer multiplied into the VCO frequency range of PLL2 (X,Y). Once locked, the chosen VCO frequency can be integer divided using the 20 bit programmable divider circuits preceding the programmable output transmitter ports. The charge pump current, feedback divider, R0, C0 and the Kvco of the internal VCO are register programmable inside the chip. Capacitors C1 and C2 and R1 are predefined fixed values.

PLL 2 Circuit Diagram (X , Y)

# X-Side PLL Chain

On the X side of the chip, XPLL1 can be supported by a single ended or differential VCXO at frequencies from 10MHz to 800MHz.. Well-chosen high frequency VCXOs can provide jitter performance levels in the 50 to 60fs range and thus locked outputs from XPLL1 can provide well under 100fs jitter performance levels in the integration band of 12 kHz to 20MHz. This frequency can then be passed through to additional output transmitters/dividers and/or be used as an input to the second stage PLL (XPLL2) to synthesize additional output frequencies at the output transmitter ports. Outputs derived from XPLL2, depending upon frequency, will generally provide jitter performance levels of < 300fs over the integrated band of 12kHz to 20 MHz.

| ADDR | BITS  | NAME      | I/0 | DEFAULT | DESCRIPTION |                                           |

|------|-------|-----------|-----|---------|-------------|-------------------------------------------|

| 0x05 | [2:0] | XPLL_Mode | RW  | 0       | XPLL Mode   |                                           |

|      |       |           |     |         | 0,5,6,7:    | Both XPLL1 and XPLL2 are power down       |

|      |       |           |     |         | 1:          | XPLL1 with sgl VCX0 -> XPLL2              |

|      |       |           |     |         | 2:          | XPLL1 with diff VCX0 -> XPLL2             |

|      |       |           |     |         | 3:          | XPLL1 with sgl VCX0; XPLL2 is power down  |

|      |       |           |     |         | 4:          | XPLL1 with diff VCXO; XPLL2 is power down |

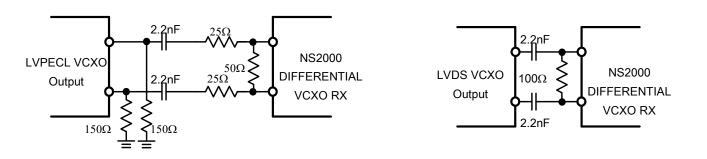

Differential VCXO termination recommendation in to pins XRX\_P and XRX\_N

Delivering a New Generation of Time and Frequency Solutions for a Connected World.

NS2000-I Data Sheet: TM139 Page 12 Rev: 10 Date: 05/31/2022

## Y-Side PLL Chain

On the Y side of the chip, YPLL1 can be supported only by a single ended VCXO at frequencies from 10MHz to 160MHz. At Output 10, the VCXO nominal frequency will bypass directly to Output 10 in order to optimize clock jitter performance with a minimal additive jitter from the chip. Output 9 is LVCMOS only which effectively acts as a buffer from the VCXO in and directly out of the chip to achieve optimal jitter (usually less than 10fs additive jitter) for ultra-low jitter applications. A well-chosen high frequency LVCMOS VCXO can provide jitter performance levels in the 60 fs range and thus locked outputs from YPLL1 can provide well under 80fs jitter performance levels in the integration band of 12kHz to 20MHz This VCXO frequency can then be passed through to additional output transmitters/dividers and/or be used as an input to the second stage PLL (YPLL2) to synthesize additional output frequencies at the output transmitter ports. Outputs derived from YPLL2, depending upon frequency, will generally provide jitter performance levels of < 300fs over the integration band of 12kHz to 20 MHz.

| ADDR | BITS  | NAME      | I/0 | DEFAULT | DESCRIPTION |                                     |

|------|-------|-----------|-----|---------|-------------|-------------------------------------|

| 0x06 | [2:0] | YPLL_Mode | RW  | 0       | YPLL Mode   |                                     |

|      |       |           |     |         | 0,5,6,7:    | Both YPLL1 and YPLL2 are power down |

|      |       |           |     |         | 1,2: YPLL1  | with sgl VCXO -> PLL2               |

|      |       |           |     |         | 3,4: YPLL1  | with sgl VCXO; YPLL2 is power down  |

## **Clock Distribution, Dividers and Drivers**

The NS2000-1PPS generates up to 23 clock outputs on ten output transmitter ports and three single ended 3.3V clock output pins driven from various sections of the chip. Output transmitter ports 1-8 are preceded by a 20 bit divider circuits (any integer value from 1-1,048,576). The divider circuits can be used regardless whether the output were generated from PLL1 or PLL2.

Output transmitter ports 1 through 8 are driven by clocks generated from PLLs 1 or 2 on either the X or Y side of the chip. Output transmitter ports 0 and 10 serve only their respective X and Y side of the chip. The output transmitter ports consist of programmable 3-in-1 transmitters that can be configured to output either (2) LVCMOS or 1 LVDS or 1 LVPECL logic signal. Output transmitters can be powered down if not in use. When using LVCMOS mode, outputs can be generated on both output pins (P and N) of the output transmitter, or, one or the other. Polarity of the LVCMOS output at each pin is controllable.

Output 10, on the Y side of the chip, has been provided for use as a low jitter buffer that directly bypasses the Y side VCXO signal in and out of the chip resulting in the least amount of additive jitter (about 10fs). This output is intended to be used for ultra-low jitter performance requirements but will have inverted phase from the outputs that are generated through the transmitter output ports.

Output 11 is a 3.3V single ended CMOS output clock that has been provided to allow for an "any frequency" output that is synthesized directly from the NS2000-1PPS NPLL's timing generator. This output, because it is digitally synthesized, will have higher jitter than Outputs 0-10. Output 11 has a frequency range of 10MHz to 80MHz and is programmed as 8kHz \* M where  $1250 \le M \le 10000$ . The NS2000-1PPS also has a 1PPS pulse generator which outputs a programmable pulse width 3.3V CMOS 1PPS signal which is also derived directly from the system's timing generator.

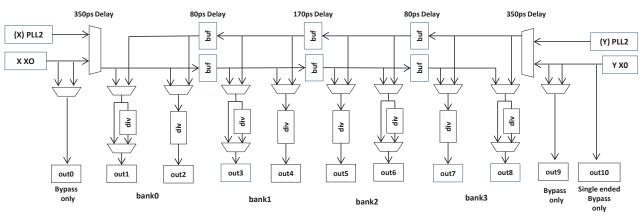

## **Output Bank Details and Constant Skew Delay Description**

Output transmitter ports 1 through 8 are divided into four output "banks". Each of the four output banks must be controlled as a unit. Bank0 (Output transmitters 1 and 2), Bank1 (Output transmitters 3 and 4), Bank2 (Output transmitters 5 and 6), and Bank3 (Output transmitters 7 and 8) represent four "banks" of outputs that can be controlled independently from each X and Y side of the chip. Either the X side or the Y side of the chip can access all four output banks, thus eliminating the requirement to use both sides X and Y in all applications. However, X and Y side clock signals must access output banks in order and must stop at the first output bank placed in use by the alternate side. For example, if X side uses banks 0, 1 and 2, Y side can only access bank 3 (outputs transmitters 1,2 and 3,4).

# Output Bank Details and Constant Skew Delay Description continued

Diagram 1 Detailed Output Banks and Ports Diagram

The skew between clock outputs is constant but will exhibit a cumulative delay relative to each other based on the clock signal traveling through MUXs and Buffers. This will be dependent upon how the output banks are configured from each X and Y side. Delay times are identified in Diagram 1. The phase skew alignment of the reference inputs to the X and Y side VCXO can be programmed to a zero level using register settings.

## Symmetry Control for low value odd dividers

Due to overall power limitations in the chip, only output transmitter circuits 2, 4, 5 and 7 have, by default, output symmetry control when dividing by a low, odd integer value. In circumstances which require dividing the VCO output frequency by values of 3, 5, 7 or 9, one of these output transmitter circuits should be used to achieve 50/50 duty cycle. When using an odd divider value of greater than nine (9), symmetry control is generally not required to maintain reasonable symmetry in the output. The output ports offering symmetry control do not allow for a direct by-pass through of the reference input frequency and require dividing at the output transmitter circuit by a minimum by 2. Output ports 1, 3, 6 and 8 can by-pass the divider circuit entirely or can divide by any integer number up to the 20bit value.

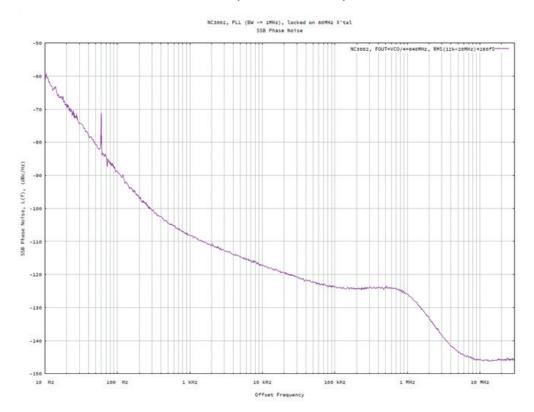

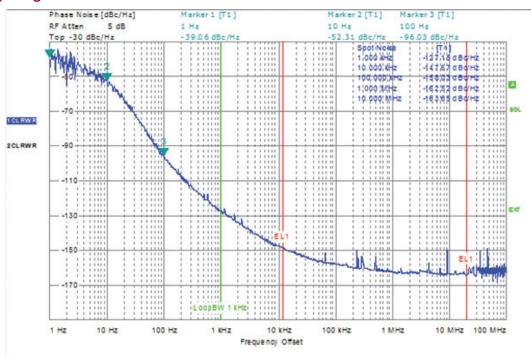

## **Output Phase Noise Characteristic Examples:**

# Phase noise generated from PLL2: 640MHz using 80MHz VCXO 260fs (12kHz-20MHz)

# Phase noise generated from PLL1(y): 122.88MHz 63fs (12kHz-20MHz) (using Connor Winfield model V7223T-122.88MHz LVCMOS 5x3.2mm VCXO)

Measurement Complete

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NS2000-I Data Sheet: TM139 Page 15 Rev: 10 Date: 05/31/2022

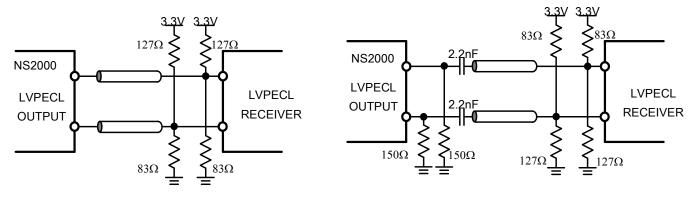

# NS2000-1PPS LVPECL Suggested Termination

**DC-Coupled LVPECL Termination**

AC-Coupled LVPECL Termination

#### **LVPECL** Current Consumption

fvco=1.244GHz, fvcxo=38.88MHz,ftcxo=20MHz

|                  |                | 10/10 00100111112,110 |                  |              |

|------------------|----------------|-----------------------|------------------|--------------|

| OUTPUT FREQUENCY | DUTY CYCLE (%) | <b>RISE TIME</b>      | CURRENT          | DIFFERENTIAL |

| (MHz)            |                | (20%~80%)(ps)         | CONSUMPTION (mA) | SWING (Vp-p) |

| 38.88            | 50.09          | 590                   | 41.69            | 1.183        |

| 103.681          | 49.97          | 570                   | 41.59            | 1.139        |

| 113.108          | 45.44          | 560                   | 41.59            | 1.148        |

| 124.417          | 49.98          | 570                   | 41.57            | 1.161        |

| 138.239          | 44.49          | 520                   | 41.53            | 1.171        |

| 155.519          | 49.98          | 530                   | 41.56            | 1.152        |

| 177.74           | 43.06          | 570                   | 41.56            | 1.163        |

| 207.362          | 50.1           | 510                   | 41.41            | 1.182        |

| 248.836          | 42             | 430                   | 41.34            | 1.095        |

| 311.054          | 50.14          | 500                   | 41.32            | 1.049        |

| 414.736          | 35.64          | 370                   | 41.53            | 0.86         |

| 622.115          | 51.05          | 270                   | 41.56            | 0.778        |

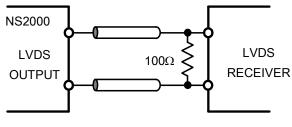

# NS2000-1PPS LVDS Suggested Termination

**DC-Coupled LVDS Termination**

AC-Coupled LVDS Termination

LVDS Current Consumption fvco=1.244GHz, fvcxo=38.88MHz,ftcxo=20MHz

| OUTPUT FREQUENCY<br>(MHz) | DUTY CYCLE (%) | <b>RISE TIME</b><br>(20%~80%)(ps) | CURRENT<br>CONSUMPTION (mA) | DIFFERENTIAL<br>SWING (Vp-p) |

|---------------------------|----------------|-----------------------------------|-----------------------------|------------------------------|

| 38.8815                   | 49.97          | 700                               | 18.18                       | 0.593                        |

| 103.68                    | 50.18          | 620                               | 18.26                       | 0.586                        |

| 113.107                   | 50.46          | 600                               | 18.26                       | 0.593                        |

| 124.414                   | 50.21          | 610                               | 18.26                       | 0.606                        |

| 138.241                   | 50.52          | 580                               | 18.26                       | 0.61                         |

| 155.52                    | 50.26          | 600                               | 18.26                       | 0.6                          |

| 177.737                   | 50.81          | 610                               | 18.26                       | 0.598                        |

| 207.363                   | 50.52          | 600                               | 18.25                       | 0.623                        |

| 248.832                   | 50.8           | 450                               | 18.25                       | 0.575                        |

| 311.05                    | 50.62          | 580                               | 18.26                       | 0.547                        |

| 414.733                   | 49.57          | 250                               | 18.27                       | 0.431                        |

| 622.108                   | 50.9           | 220                               | 18.24                       | 0.378                        |

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NS2000-I Data Sheet: TM139 Page 16 Rev: 10 Date: 05/31/2022

# NS2000-1PPS Register Table

| ADDR      | BITS   | NAME             | I/0  | DEFAULT | DESCRIPTION                                                    |

|-----------|--------|------------------|------|---------|----------------------------------------------------------------|

| 0x00~0x01 | [15:0] | Chip_ID          | R    | 0x2D00  | Chip ID, it reflects the current product ID                    |

| 0x02      | [7:0]  | Chip_REV         | R    | 0x02    | Chip Revision                                                  |

| 0x03      | [7:0]  | Chip_Sub_REV     | R    | 0x03    | Chip Sub revision                                              |

| 0x04      | [7:0]  | NPLL_FW_REV      | R    | 0x04    | NPLL's Firmware Revision                                       |

| 0x05      | [2:0]  | XPLL_Mode        | RW   | 0       | XPLL Mode                                                      |

|           |        | _                |      |         | 0,5,6,7: Both XPLL1 and XPLL2 are power down                   |

|           |        |                  |      |         | 1: XPLL1 with sgl VCXO -> XPLL2                                |

|           |        |                  |      |         | 2: XPLL1 with diff VCXO -> XPLL2                               |

|           |        |                  |      |         | 3: XPLL1 with sgl VCX0; XPLL2 is power down                    |

|           |        |                  |      |         | 4: XPLL1 with diff VCX0; XPLL2 is power down                   |

| 0x06      | [0.0]  | YPLL_Mode        | RW   | 0       | YPLL Mode                                                      |

| 0000      | [2:0]  | TFLL_WOUR        | n vv | 0       |                                                                |

|           |        |                  |      |         | 0,5,6,7: Both YPLL1 and YPLL2 are power down                   |

|           |        |                  |      |         | 1,2: YPLL1 with sgl VCX0 -> PLL2                               |

|           |        |                  |      |         | 3,4: YPLL1 with sgl VCX0; YPLL2 is power down                  |

| 0x07~0x08 | [15:0] | INTR_EVENT       | RW   | 0       | Interrupt Event                                                |

|           |        |                  |      |         | bit[0] REG(NPLL_MODE) value changed                            |

|           |        |                  |      |         | bit[15~1] ~ RSVD ~                                             |

| 0x09~0x1F |        | ~ RSVD ~         |      |         |                                                                |

| 0x20      | [2:0]  | NPLL_MODE        | R    |         | NPLL_MODE                                                      |

|           |        |                  |      |         | 0: HOLDOVER_LOS                                                |

|           |        |                  |      |         | 1: FLL_LOCKING                                                 |

|           |        |                  |      |         | 2: PHASE_ReBUILDING                                            |

|           |        |                  |      |         | 3: PLL_FAST_LOCKING                                            |

|           |        |                  |      |         | 4: PLL_LOCKING                                                 |

|           |        |                  |      |         | 5: PLL_LOCKED                                                  |

|           |        |                  |      |         | 6,7: ~ RSVD ~                                                  |

| 0x21~0x22 | [15:0] | NPLL_INFO_EX     | R    |         | 16-bit NPLL Extra Information. It could have different meaning |

| 0721~0722 | [15.0] |                  | n    |         | -                                                              |

|           |        |                  |      |         | in different NPLL_MODE                                         |

|           |        |                  |      |         | if in FLL_LOCKING mode                                         |

|           |        |                  |      |         | bit[14:0] countdown of soaking time, unit(S)                   |

|           |        |                  |      |         | bit[15] = 0                                                    |

|           |        |                  |      |         | if in PLL_FAST_LOCKING, PLL_LOCKING, or PLL_LOCKED mode.       |

|           |        |                  |      |         | bit[14:0] leaking bucket's level                               |

|           |        |                  |      |         | bit[15] == 1                                                   |

| 0x23~0x28 | [47:0] | PHe_RAW          | R    |         | Raw phase error between 1PPS output and 1PPS input.            |

|           |        |                  |      |         | 48-bit 2's complement. Unit in nS.                             |

| 0x29~0X2E | [47:0] | PHe_CALI         | R    |         | Calibrated phase error between 1PPS output and 1PPS input.     |

|           |        |                  |      |         | 48-bit 2's complement. Unit in nS.                             |

| 0x2F~0x34 | [47:0] | OUT_FF0          | R    |         | Output's normalized fractional frequency offset to calibrated  |

|           | J      | ··· <b>_</b> ··• |      |         | MCLK frequency. 48-bit 2's complement. Unit in ppt (=10-12)    |

| 0x35      | [0]    | NPLL_START       | R/W  | 0       | Write 1 to this register to start NPLL. Once NPLL was started, |

| 5,000     | [~]    | ==_0/////        |      |         | it could be turned off only by IC reset or power cycle.        |

|           |        |                  |      |         | NPLL's run-time manual control                                 |

|           |        |                  |      |         | bit[0]: forced into manual LOS/HOLDOVER                        |

|           |        |                  |      |         | 1: enable                                                      |

|           |        |                  |      |         | 0: disable                                                     |

|           |        |                  |      |         | bit[1]: to stop at PLL_FAST_LOCKING mode                       |

|           |        |                  |      |         | 1: enable                                                      |

|           |        |                  |      |         | 0: disable                                                     |

|           |        |                  |      |         | bit[7:2]: ~RSVD~                                               |

| 0x36      | [7:0]  | NPLL_RT_CTRL     | R/W  | 0       | <ps.1></ps.1>                                                  |

| 2,00      | [,]    |                  |      |         | If set to enable to stop at PLL_FAST_LOCKING mode,             |

|           |        |                  |      |         | NPLL will not move to PLL_LOCKING/LOCKED mode.                 |

|           |        |                  |      |         | This will force NPLL to stay using PLL_FAST_LOCKING's          |

|           |        |                  |      |         | parameters until this feature is disabled                      |

|           |        |                  |      |         | ן אמומוווכובוס טווטו גוווס ובמנטוב וס טוסמטובטו                |

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NS2000-I Data Sheet: TM139 Page 17 Rev: 10 Date: 05/31/2022

| ADDR      | BITS    | NAME                      | I/0 | DEFAULT        | DESCRIPTION                                                                              |

|-----------|---------|---------------------------|-----|----------------|------------------------------------------------------------------------------------------|

| 0x37      | [7:0]   | NPLL_FLL_PARA             | R/W | 0              | NPLL FLL_LOCKING mode parameters                                                         |

|           |         |                           |     |                | bit[1:0] low-passed filter's band index                                                  |

|           |         |                           |     |                | (0) 179 mHz                                                                              |

|           |         |                           |     |                | (1) 90 mHz                                                                               |

|           |         |                           |     |                | (2) 45 mH                                                                                |

|           |         |                           |     |                | (3) 22 mHz                                                                               |

|           |         |                           |     |                |                                                                                          |

| 0.00.0.00 | [4.4.0] |                           | DAM |                |                                                                                          |

| 0x38~0x39 | [14:0]  | NPLL_FLL_SOAKTIME         | R/W | 0              | NPLL FLL_LOCKING mode soaking time. 15-bit. Unit in second.                              |

|           |         |                           |     |                | bit[14:0] soaking time, unit(second)                                                     |

|           |         |                           |     |                | bit[15] ~ RSVD ~                                                                         |

| 0x3A      | [7:0]   | NPLL_PLL_PARA             | R/W | 0              | NPLL PLL_FAST_LOCKING, PLL_LOCKING, PLL_LOCKED                                           |

|           |         |                           |     |                | parameter                                                                                |

|           |         |                           |     |                | bit[2:0] Loop bandwidth in PLL_LOCKING/LOCKED mode                                       |

|           |         |                           |     |                | bit[5:3] Loop bandwidth in PLL_FAST_LOCKING mode                                         |

|           |         |                           |     |                | bit[7:6] Damping factor                                                                  |

|           |         |                           |     |                | Loop bandwidth:                                                                          |

|           |         |                           |     |                |                                                                                          |

|           |         |                           |     |                | (0) 50 mHz                                                                               |

|           |         |                           |     |                | (1) 25 mHz                                                                               |

|           |         |                           |     |                | (2) 13 mHz                                                                               |

|           |         |                           |     |                | (3) 6.3 mHz                                                                              |

|           |         |                           |     |                | (4) 3.1 mHz                                                                              |

|           |         |                           |     |                | (5) 1.6 mHz                                                                              |

|           |         |                           |     |                | (6) 0.78 mHz                                                                             |

|           |         |                           |     |                | (7) 0.39 mHz                                                                             |

|           |         |                           |     |                |                                                                                          |

|           |         |                           |     | Damping factor |                                                                                          |

|           |         |                           |     | (0) 0.7        |                                                                                          |

|           |         |                           |     |                | (1) 1.4                                                                                  |

|           |         |                           |     | (2) 2.0        |                                                                                          |

|           |         |                           |     |                | (3) 3.5                                                                                  |

| 0x3B~0x3C | [14:0]  | NPLL_LEAKBUCK_THRESHOLD   | R/W | 0              | NPLL PLL's leaking bucket threshold. Unit(nS).                                           |

|           |         |                           |     | -              | bit[14:0] phase error threshold. unit(nS)                                                |

|           |         |                           |     |                | bit[15] ~ RSVD ~                                                                         |

| 0x3D~0x3E | [14.0]  |                           | DAM | 0              | NPLL PLL'S leaking bucket size in PLL_FAST_LOCKING mode                                  |

| UX3D~UX3E | [14:0]  | NPLL_LEAKBUCK_SIZE_FAST   | R/W | 0              | -                                                                                        |

|           |         |                           |     |                | bit[14:0] bucket size                                                                    |

|           |         |                           |     |                | Obit[15] ~ RSVD ~                                                                        |

| 0x3F~0x40 | [14:0]  | NPLL_LEAKBUCK_SIZE_NORMAL | R/W | 0              | NPLL PLL's leaking bucket size in PLL_LOCKING and PLL_LOCKED                             |

|           |         |                           |     |                | mode                                                                                     |

|           |         |                           |     |                | bit[14:0] bucket size                                                                    |

|           |         |                           |     |                | bit[15] ~ RSVD ~                                                                         |

|           |         |                           |     |                | NPLL's soft phase error tolerance. The phase error tolerance                             |

| 0x41~0x42 | [14:0]  | NPLL_PHe_SOFT_TOLERANCE   | R/W | 0              |                                                                                          |

|           |         |                           |     |                | or re-entry from LOS/HOLDOVER mode. Unit in nS.                                          |

|           |         |                           |     |                | bit[14:0] soft tolerance, unit(nS)                                                       |

| 0x43~0x44 | [14:0]  | NPLL_PHe_HARD_TOLERANCE   | R/W | 0              | NPLL's hard phase error tolerance. Phase error tolerance of                              |

|           | [1.1.0] |                           |     | ř              | the LOL thresh hold. Unit in nS.                                                         |

|           |         |                           |     |                | bit[14:0] hard tolerance, unit(nS)                                                       |

|           |         |                           |     |                | NPLL's phase align configuration                                                         |

|           |         |                           |     |                | bit[0]: Phase aligned to 1PPS on XPLL: 1=YES, 0=N0                                       |

|           |         |                           |     |                | bit[1]: Phase aligned to 1PPS on YPLL: 1=YES, 0=N0                                       |

|           |         |                           |     |                |                                                                                          |

|           |         |                           |     |                | bit[2, 3]: DNC                                                                           |

|           |         |                           |     |                | bit[4]: Align-in-Wide-Speed mode: 1=0N, 0=0FF                                            |

|           |         |                           |     |                | <pre>bit[5]: NPLL_PD_CALI resolution: 1=COARSE, 0=FINE</pre>                             |

| 0x45      | [1:0]   | NPLL_ALIGNED_PATH         | R/W | 0              | bit[7:6]: LEAKBUCK_FILL_RATE: rate=(n+1)=1~4                                             |

|           |         |                           |     |                | <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> |

|           |         |                           |     |                | NPLL_PD_CALI resolution, see REG(NPLL_RT_PD_CALI)                                        |

|           |         |                           |     |                | <pre>vpcl_pd_cali resolution, see reg(vpcl_ri_pd_cali) <ps.2></ps.2></pre>               |

|           |         |                           |     |                |                                                                                          |

|           |         |                           |     |                | •                                                                                        |

|           |         |                           |     |                | LEAKBUCK_FILL_RATE is used when the phase error is                                       |

|           |         |                           |     |                | •                                                                                        |

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NS2000-I Data Sheet: TM139 Page 18 Rev: 10 Date: 05/31/2022

| ADDR      | BITS   | NAME                     | I/0 | DEFAULT | DESCRIPTION                                                                                                                                                               |

|-----------|--------|--------------------------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |        |                          |     |         | The frequency of output to align to 1PPS output. Use the common division of the frequencies if more than 1 output. 17-bit. Unit in 8kHz.<br>bit [16:0] n, freq = 8kHz x n |

|           |        |                          |     |         | bit [47:17] must be zero                                                                                                                                                  |

| 0x46~4B   | [47:0] | NPLL_RT_ALIGNED_OUT_FREQ | R/W | 0       | <pre><ps.1></ps.1></pre>                                                                                                                                                  |

|           | []     |                          |     |         | Setting the aligned output frequency to zero means 1PPS output pulse<br>does not need to phase align to any other clock outputs<br><ps.2></ps.2>                          |

|           |        |                          |     |         | This register used to be NPLL's configuration register and became NPLL's run-time register since firmware revision 0x03.                                                  |

|           |        |                          |     |         | The maximal phase shifting speed to compensate the previous PBO (phase build-out) phase error while adjusting the phase alignment from FLL to PLL_FAST_LOCKING            |

|           |        |                          |     |         | Align-in-Wide-Speed mode is OFF:                                                                                                                                          |

|           |        |                          |     |         | bit[7:0] index=0~255; (band=0)                                                                                                                                            |

| 0x4C      | [7:0]  | NPLL_PHASE_SHIFT_SPEED   | R/W | 0       | Align-in-Wide-Speed mode is ON:                                                                                                                                           |

|           |        |                          |     |         | bit[7:6] band= $0 \sim 3$                                                                                                                                                 |

|           |        |                          |     |         | bit[5:0] index=0~63                                                                                                                                                       |

|           |        |                          |     |         | maximal shift speed = index x (16band) x (10 $pS/S$ )                                                                                                                     |

|           |        |                          |     |         | User specified phase detector offset calibration, to cover 1PPS input's                                                                                                   |

|           |        |                          |     |         | quantization error and cable latency delay. 16-bit 2's complement.                                                                                                        |

|           |        |                          |     |         | <ul> <li>- if NPLL_RT_PD_CALI resolution = FINE</li> </ul>                                                                                                                |

| 0x4D~0x4E | [15:0] | NPLL_RT_PD_CALI          | R/W | 0       | - unit (2 pS), coverage = $\pm$ 65.536 nS                                                                                                                                 |

|           |        |                          |     |         | - cover more than 13-meter cable latency delay                                                                                                                            |

|           |        |                          |     |         | <ul> <li>- if NPLL_RT_PD_CALI resolution = COARSE</li> </ul>                                                                                                              |

|           |        |                          |     |         | - unit(50 pS), coverage = $\pm$ 1.638 uS                                                                                                                                  |

|           |        |                          |     |         | - cover more than 300-meter cable latency delay                                                                                                                           |

|           |        |                          |     |         | User specified MCLK frequency offset calibration. 28-bit 2's complement.<br>Unit in (0.851495 ppt)                                                                        |

| 0x4F~0x54 | [47:0] | NPLL_RT_MCLK_CALI        | R/W | 0       | bit [27:0] calibration offset, 2's complement unit (0.851495 ppt)<br>bit [47:28] must be zero                                                                             |

|           |        |                          |     |         | <ps.1></ps.1>                                                                                                                                                             |

|           |        |                          |     |         | Writing a negative value will decrease the frequency.                                                                                                                     |

|           |        |                          |     |         | Writing a positive value will increase the frequency                                                                                                                      |

| 0x55~0x5F |        | ~ RSVD                   |     |         |                                                                                                                                                                           |

| 0x60~0x61 | [12:0] | XPLL1_REF_FREQ_M         | RW  | 1       | NPLL synthesizes XPLL1's reference clock with frequency of<br>(M *8kHz). 13-bit M value is set by this register.                                                          |

|           |        |                          | _   |         | 1 <= M <= 5000                                                                                                                                                            |

| 0x62      |        | ~ RSVD ~                 |     |         |                                                                                                                                                                           |

| 0x63~0x64 | [14:0] | XPLL1_FB_DIV             | RW  | 0       | XPLL1 15-bit feedback divider value; Value 0 means disable                                                                                                                |