# NTC1012 Zero Delay Clock Buffer with PWM Message Forwarding

### Overview

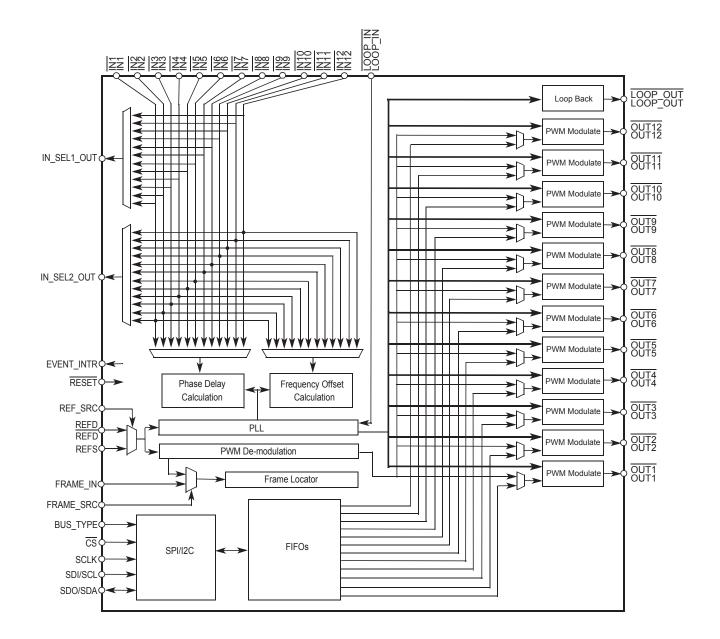

The NTC1012 is a highly integrated multi-function synchronizing IC. It combines the functionality of a low jitter, zero delay clock buffer, a multi output clock generator, an integrated pulse width modulation (PWM) messaging capability and an internal phase detector. The source of the PWM message transmitted onto the output clock signals can be chosen from either of two options: the de-modulation of a PWM message on the incoming reference clock or written directly from data generated and supplied by the user. The NTC1012 allows the user to calculate and compare both phase delay as well as the frequency offset

between a source reference and one of 12 inputs (IN1 - IN12). Two of the 12 differential inputs can be selected independently and converted to two single-ended outputs to support the phase and frequency offset measurement and comparison.

The NTC1012 provides twelve 3.3V LVDS output ports (OUT1 – OUT12) that generate clock signals that are phase locked and phase aligned with the reference input. One of the rising edges of the reference clock is used to identify the SYNC position, which is also the position to begin sending PWM data. This position can be determined from either the FRAME\_IN signal or from PWM data carried by the reference clock. The NTC1012 is capable of either de-modulating a formatted PWM message modulated onto the 25MHzor 10MHz input reference or using the data supplied by user to modulate a PWM message onto each of the twelve output signals.

Twelve LVDS output transmitter ports each have a dedicated FIFO to store user supplied data allowing the final output PWM message to be generated from either the dedicated FIFO or from the de-modulated PWM message obtained from the reference input. The user can individually control the message within each FIFO/output or send a global message to all twelve outputs at once. Communication and interrogation of system activity is available through either I2C or SPI bus interfaces.

| Bulletin | TM137       |

|----------|-------------|

| Revision | 00          |

| Date     | 06 Jan 2019 |

D

Α

Δ

## NTC1012 Functional Port Diagram

### **Specifications**

| Parameter                       | Specification                                          |

|---------------------------------|--------------------------------------------------------|

| Voltage                         | 3.3V ±5% and 1.8Vdc ±5%                                |

| Power                           | 20-30 mA per LVDS output depending on signal amplitude |

| Temperature                     | -40 to 85°C Industrial temp range operation            |

| Frame Reference Frequency       | 1, 2, 4 kHz or 8 kHz                                   |

| XI/XO Input                     | Single ended clock signal or fundamental mode crystal  |

| REF_IN/Output Frequency Options | 25 MHz or 10 MHz                                       |

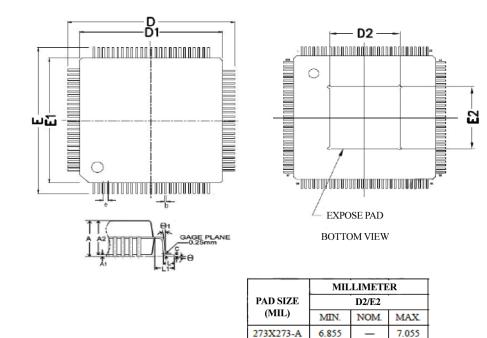

| Dimensions                      | 14x 14 x 1.4 mm 128 pin LQFP package                   |

|                                 |                                                        |

## NTC1012 General Description

The NTC1012 is a highly integrated multi-function synchronizing IC. It combines the functionality of a low jitter zero delay clock buffer, a multi output clock generator, an integrated pulse width modulation (PWM) messaging capability, an internal phase detector to support the measurement of phase delay and fractional frequency offset calculation and generation of two single-ended outputs selected from the 12 differential inputs (In\_1-In\_12). The NTC1012 offers five primary functions:

#### Zero-Delay Clock Buffer

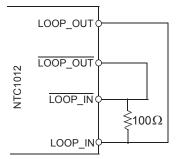

The NTC1012 requires an external loop back clock to achieve its zero-delay clock buffer requirement. The output of LOOP\_OUT should be connected to LOOP\_IN externally. An internal PLL locks onto the 25MHZ REF\_IN reference and compares the phase difference between the input of FRAME\_IN and LOOP\_IN. It then adjusts the phase of LOOP\_OUT and outputs OUT1 - OUT12 globally to maintain the minimum phase skew between FRAME\_IN and all output signals. The skew can also be programmatically controlled.

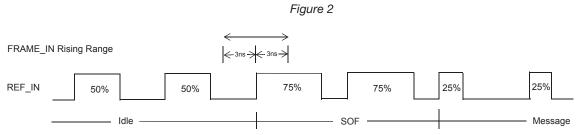

The 25MHz REF\_IN clock may contain a PWM message that can be forwarded to each or all output ports. If the PWM message needs to be de-modulated and modulated onto any output ports, the rising edge of SOF (start of frame) clock cycle at REF\_IN need to be aligned with the rising edge of FRAME\_IN within +-3ns as shown in Fig 2. The SOF is two 75% high time clock cycles after a 50% duty (idle cycle) clock cycle from REF\_IN. If none of the outputs need to carry PWM message from REF\_IN, the phase relation of REF\_IN and FRAME\_IN can be arbitrary

Message Forwarding from Output Clocks (OUT1 - OUT12) with PWM

Each or all of twelve LVDS output clocks can carry a message via PWM to the receiving side. Each output can carry a different message. The message source for each output can be from either de-modulating a message that had been modulated onto the input reference clock (REF\_IN) or written directly from user generated and supplied data that is updated periodically.

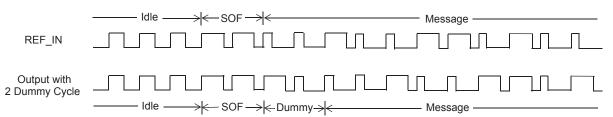

If the output message source is selected to come from a de-modulated message on the reference clock input (REF\_IN), there is a requirement for dummy cycles to be inserted between the SOF and the message. This is shown in Fig 3. The number of dummy cycles created is programmable from 2 to 8. The duty cycle of each dummy cycle is also programmable.

### **REF\_IN to Output PWM Forward**

Figure 3

When the message is taken from user supplied data, the modulation format is programmable. Message zero or one can be defined as 25% or 75% high of one clock cycle. 50% high time is reserved for "idle" cycle. Each bit can be either modulated by one clock cycle or two clock cycles. If the message is modulated by two clock cycles, the sum of these two clock cycle's high time will be 50% of two clock periods. The bit transmitted sequence within a byte can be either LSB or MSB.

When the output message comes from user supplied data, the data is updated periodically in each frame. Messages written in the Nth frame period will be sent out in the (N+1)th frame period. The number of bytes to be sent in the (N+1)th frame period is determined by the number of bytes written into the buffer during Nth frame period. After the number of programmed bytes is sent, the rest of the clock cycles in the frame will be 50% duty clock cycle. Each output port has an individual double-buffer for the user message, so the output message can be different for each output. The user can update one buffer while the other buffer is transmitting. The data can also be read back for checking. If the message for all outputs are the same, there is a global update mechanism so the user does not need to write the same data to each of the 12 output ports individually.

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NTC1012 Data Sheet: TM137 Page 3 Rev: 00 Date: 01/06/19

### NTC1012 General Description continued

#### Frequency Offset Calculation Between FRAME\_IN and Inputs (IN1 - IN12)

The NTC1012 allows the user to calculate the fractional frequency offset between a selected (programmable) clock input and the given framing reference (FRAME\_IN). The input to be checked must be 8kHz clock. The frequency offset checking period is programmable in 1, 2, 4 or 8 seconds. When the checking period is complete, NTC1012 will assert one of event status and report the frequency offset in 10 ppb unit.

- 1. Calculates the fractional frequency offset of one (programmable) of the 12 clock inputs (IN1~IN12).

- 2. Programmable observation period of 1/2/4/8 seconds

- 3. Fractional frequency offset will be calculated as the phase drifted over the observation period.

- 4. Fractional frequency offset difference measurement is provided in 10ppb units.

- 5. An interrupt will be trigged to inform the readiness of the fractional frequency offset result.

#### Phase Delay Measurement from FRAME\_IN to Inputs (IN1 - IN12)

NTC1012 can measure the phase delay from FRAME\_IN to the inputs. The measurement can be done with one input at a time. The input to be measured must be the same frequency as FRAME\_IN. The number of measurements is programmable in 1, 2, 4, 8 or 16 times. When the measurement is complete, NTC1012 will assert one of the event status register and report each measurement and the average in ps unit.

The NTC1012 allows the user to measure the phase difference between a selected (programmable) clock input and the given framing reference (FRAME\_IN).

- 1. Measures the phase difference between one (programmable) of the 12 clock inputs (IN1~IN12) versus the framing reference (FRAME\_IN)

- 2. Averages and stores the phase differences of multiple successive measurements

- 3. Programmable number (1/2/4/8/16) of successive measurements to be average and stored

- 4. Phase difference measurement is provided in ps units.

- 5. An interrupt will be trigged to inform the readiness of the phase measurement results and their average value

#### **Outputs from Selected Inputs (IN1 - IN12)**

The NTC1012 allows the user to generate two single ended bypass outputs to assist in the frequency and phase measurement process. The two selected inputs can be selected through register programming from any of the up to 12 LVDS clock inputs (IN1~IN12) it receives. The two selected clock inputs are then bypassed through the IC and output as single-ended 3.3V LVCMOS signals the same frequency at pins (IN\_SEL\_OUT1) and (IN\_SEL\_OUT2).

## NTC1012 Serial Interface

The NTC1012 supports both SPI or I2C serial interfaces for the user to communicate with the IC. The user can select which method they would like to interface with the IC by setting the pin BUS\_TYPE to the appropriate logic level to select the bus type. When BUS\_TYPE pin is set high, SPI is active, otherwise I2C is active by default

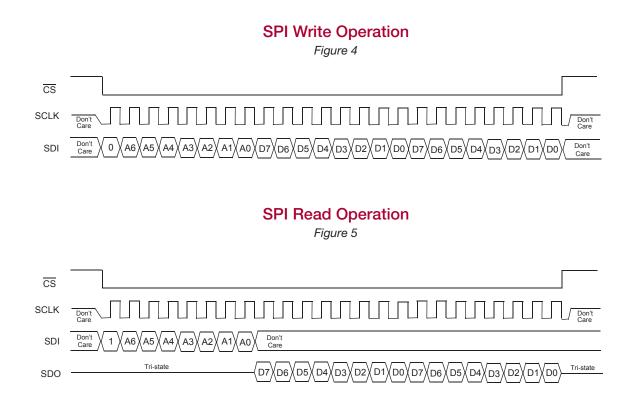

#### SPI Mode Operation

In SPI mode, single or multiple byte transfers are supported. The address and data bytes are sent in MSB first. A write or a read operation to the NTC1012 is initiated by pulling CS low. Bit 7 of first byte indicates the operation type, bit 6 - 0 of first byte indicates the address of first byte of data. For multiple byte access, the internal address will keep increment by one for each byte access. Fig 4 shows the write operation.

### NTC1012 Serial Interface continued

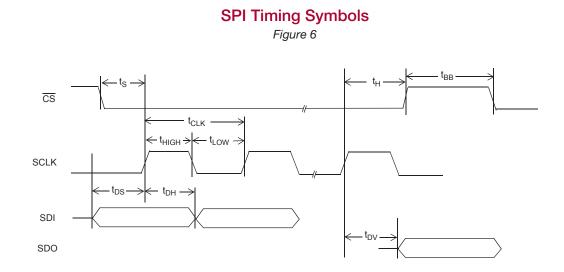

SPI timing symbols are shown in Fig 6, and timing parameters are shown in Table 1.

#### SPI Timing Parameters Table 1

able I

| Parameters        | Description                                 | Min | Тур | Max | Unit |

|-------------------|---------------------------------------------|-----|-----|-----|------|

| <sup>t</sup> CLK  | Period of SCLK                              | 40  | -   | -   | ns   |

| <sup>t</sup> HIGH | SCLK high time                              | 15  | -   | -   | ns   |

| <sup>t</sup> LOW  | SCLK low time                               | 15  | -   | -   | ns   |

| ťS                | Setup time between CS to SCLK               |     |     |     |      |

|                   | rising edge for initiating the transmission | 10  | -   | -   | ns   |

| tH                | Hold time between CS to SCLK                |     |     |     |      |

|                   | rising edge for ending the transmission     | 12  | -   | -   | ns   |

| <sup>t</sup> DS   | Setup time between SDI and SCLK rising edge | 10  | -   | -   | ns   |

| <sup>t</sup> DH   | Hold time between SDI and SCLK rising edge  | 7   | -   | -   | ns   |

| <sup>t</sup> DV   | SCLK to SDO data valid time                 | -   | -   | 20  | ns   |

| <sup>t</sup> BB   | Minimum gap for back to back transmission   | 20  | -   | -   | ns   |

NTC1012 Data Sheet: TM137 Page 6 Rev: 00 Date: 01/06/19

## **NTC1012 Electrical Specification**

## **Recommended Operating Conditions**

|                   | Table 2           |                                                                                                                                                                                             |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | Symbol            | Min                                                                                                                                                                                         | Тур                                                                                                                                                                                                                                    | Max                                                                                                                                                                                                                                                                                                                                                                                                 | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TA                | -40               |                                                                                                                                                                                             | 25 85                                                                                                                                                                                                                                  | °C                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TJ <sub>MAX</sub> | -                 | -                                                                                                                                                                                           | 125                                                                                                                                                                                                                                    | °C                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   | DVDD18            | 1.70                                                                                                                                                                                        | 1.80                                                                                                                                                                                                                                   | 1.90                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | DVDD33            | 3.00                                                                                                                                                                                        | 3.30                                                                                                                                                                                                                                   | 3.60                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VDD33_PLL         | 3.15              |                                                                                                                                                                                             | 3.30 3.45                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDD33_FB          | 3.15              |                                                                                                                                                                                             | 3.30 3.45                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   |                   |                                                                                                                                                                                             |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   | VDD33_TX          | 3.15                                                                                                                                                                                        | 3.30                                                                                                                                                                                                                                   | 3.45                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   |                   |                                                                                                                                                                                             |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   | VDD33_RX          | 3.15                                                                                                                                                                                        | 3.30                                                                                                                                                                                                                                   | 3.45                                                                                                                                                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -                 | TJ <sub>MAX</sub> | Symbol           TA         -40           TJ <sub>MAX</sub> -           DVDD18         DVDD33           VDD33_PLL         3.15           VDD33_FB         3.15           VDD33_TX         - | Symbol         Min           TA         -40           TJ <sub>MAX</sub> -           DVDD18         1.70           DVDD33         3.00           VDD33_PLL         3.15           VDD33_FB         3.15           VDD33_TX         3.15 | Symbol         Min         Typ           TA         -40         25         85           TJ_MAX         -         -         125           DVDD18         1.70         1.80           DVDD33         3.00         3.30           VDD33_PLL         3.15         3.30         3.45           VDD33_FB         3.15         3.30         3.45           VDD33_TX         3.15         3.30         3.45 | Symbol         Min         Typ         Max           TA         -40         25         85         °C           TJ <sub>MAX</sub> -         -         125         °C           DVDD18         1.70         1.80         1.90           DVDD33         3.00         3.30         3.60           VDD33_PLL         3.15         3.30         3.45         V           VDD33_FB         3.15         3.30         3.45         V           VDD33_TX         3.15         3.30         3.45         V |

### **DC Characteristics**

Table 3

| Parameters                                      | Symbol              | Тур | Max | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|

| Digital Core Supply Current                     | <sup>I</sup> DVDD18 | 60  | 57  | mA   |

| Digital IO Supply Current                       | <sup>I</sup> DVDD33 | 2   | 3   | mA   |

| PLL Supply Current                              | VDD33_PLL           | 35  | 39  | mA   |

| Power Supply Current for Internal LDO for PLL   |                     |     |     |      |

| Feedback Circuit                                | VDD33_FB            | 49  | 54  | mA   |

| Power Supply Current for Internal LDO and       |                     |     |     |      |

| OUT1 - OUT12 Transmitter                        | VDD33_TX            | 262 | 290 | mA   |

| Power Supply Current for Internal LDO and REFS, |                     |     |     |      |

| REFD, LOOP_IN and IN1 - IN12 Receiver           | VDD33_RX            | 168 | 186 | mA   |

#### LVDS Input Specification Table 4

| Parameters                      |   | Min | Тур  | Max | Unit |

|---------------------------------|---|-----|------|-----|------|

| Input Common Mode Voltage       | 0 | -   | 1.73 | V   |      |

| Input Differential Mode Voltage |   | 100 | -    | 800 | mV   |

| Maximum Input Voltage           |   | -   | -    | 5.5 | V    |

| Capacitance                     |   | -   | 0.4  | -   | pF   |

#### FRAME\_IN Specification Table 5

| Parameters            | Min   | Тур | Max   | Unit |

|-----------------------|-------|-----|-------|------|

| LVCMOS Input Voltage  | -0.3  | -   | 3.6   | V    |

| Input Low Voltage     | -     | -   | 1.823 | V    |

| Input High Voltage    | 1.425 | -   | -     | V    |

| Maximum Input Voltage | -     | -   | 5.5   | V    |

| Input Leakage Current | -     | -   | ±1    | uA   |

| Capacitance           | -     | 0.4 | -     | pF   |

Delivering a New Generation of Time and Frequency Solutions for a Connected World.

NTC1012 Data Sheet: TM137 Page 7 Rev: 00 Date: 01/06/19

## **Electrical Specification continued**

#### LVCMOS Input Specification Table 6

| Parameters            | Min  | Тур    | Max | Unit |

|-----------------------|------|--------|-----|------|

| LVCMOS Input Voltage  | -0.3 | -      | 3.6 | V    |

| Input Low Voltage     | -0.3 | -      | 0.8 | V    |

| Input High Voltage    | 2    | -      | 3.6 | V    |

| Maximum Input Voltage | -    | -      | 5.5 | V    |

| Input Leakage Current | -    | -      | ±1  | uA   |

| Capacitance           | -    | 2.6647 | -   | рF   |

### LVDS Output Specification Table 7

| Parameters                       | Min      | Тур      | Max     | Unit | Note       |

|----------------------------------|----------|----------|---------|------|------------|

| Output Common Mode Voltage       | 1.748    | 1.974    | 2.173   | V    |            |

| Output Differential Mode Voltage | 635      | 703      | 784     | mV   |            |

| Rise and Fall Time (20% - 80%)   | 88.4/125 | 99.3/121 | 155/135 | pS   | 1pF C-Load |

#### LVCMOS Output Specification Table 8

| Parameters            | Min  | Тур  | Max  | Unit |

|-----------------------|------|------|------|------|

| LVCMOS Output Voltage | 0    | -    | 3.6  | V    |

| Output Low Voltage    | -    | -    | 0.4  | V    |

| Output High Voltage   | 2.4  | -    | -    | V    |

| Output Low Current    | 11.5 | 17.6 | 23.2 | mA   |

| Output High Current   | 12.7 | 25.6 | 42.5 | mA   |

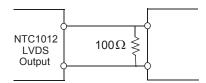

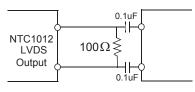

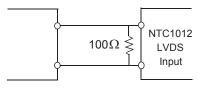

### Input Output Termination Recommendations

DC Coupled LVDS Output

AC Coupled LVDS Output

DC Coupled LVDS Input

DC Coupled Loop Back Connection

Delivering a New Generation of Time and Frequency Solutions for a Connected World. NTC1012 Data Sheet: TM137 Page 9 Rev: 00 Date: 01/06/19

NTC1012 Data Sheet: **TM137** Page **10** Rev: **00** Date: **01/06/19**

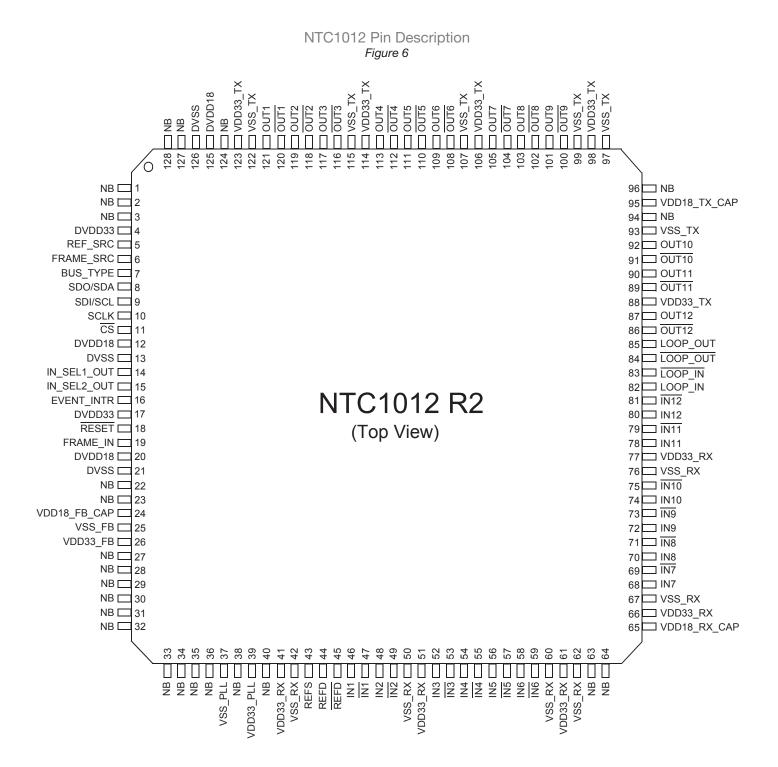

## **Pin Descriptions**

| Pin# | Name         | Туре   | IO | Description                                                                                 |

|------|--------------|--------|----|---------------------------------------------------------------------------------------------|

| 5    | REF_SRC      | LVCMOS |    | Select reference source, 0: REFS, 1: REFD/REFD                                              |

| 6    | FRAME_SRC    | LVCMOS |    | Select frame input source, 0: FRAME_IN, 1: reference PWM data                               |

| 7    | BUS_TYPE     | LVCMOS |    | Select bus mode, 0: I2C, 1: SPI                                                             |

| 8    | SD0/SDA      | LVCMOS | 10 | SDO pin when bus mode is SPI, SDA pin when bus mode is I2C                                  |

| 9    | SDI/SCL      | LVCMOS |    | SDI pin when bus mode is SPI, SCL pin when bus mode is I2C                                  |

| 10   | SCLK         | LVCMOS |    | CLK pin when SPI bus mode is used                                                           |

| 11   | CS           | LVCMOS |    | Chip select pin when SPI bus mode is used                                                   |

| 14   | IN_SEL1_OUT  | LVCMOS | 0  | Selected output from IN1 - IN12                                                             |

| 15   | IN SEL2 OUT  | LVCMOS | 0  | Selected output from IN1 - IN12                                                             |

| 16   | EVENT_INTR   | LVCMOS | 0  | Assert high to notify pre-defined events                                                    |

| 18   | RESET        | LVCMOS |    | Assert low to reset IC, minimal low pulse is 1 us                                           |

| 19   | FRAME_IN     | LVCMOS |    | 100Hz - 8kHz frame input signal                                                             |

| 43   | REFS         | LVCMOS |    | 25MHz single-ended reference clock with optional PWM message                                |

| 44   | REFD         | LVDS   |    | Along with REFD, it is LVDS differential input for 25MHz reference clock with optional      |

|      |              | -      |    | PWM message                                                                                 |

| 45   | REFD         | LVDS   |    | Complemental input signal of REFD                                                           |

| 46   | IN1          | LVDS   |    | Along with IN1, it is LVDS differential input from 100Hz - 8kHz signal                      |

| 47   | IN1          | LVDS   |    | Complemental input signal of IN1                                                            |

| 48   | IN2          | LVDS   |    | Along with IN2, it is LVDS differential input from 100Hz - 8kHz signal                      |

| 49   | IN2          | LVDS   |    | Complemental input signal of IN2                                                            |

| 52   | IN3          | LVDS   |    | Along with IN3, it is LVDS differential input from 100Hz - 8kHz signal                      |

| 53   | IN3          | LVDS   |    | Complemental input signal of IN3                                                            |

| 54   | IN4          | LVDS   |    | Along with IN4, it is LVDS differential input from 100Hz - 8kHz signal                      |

| 55   | ĪN4          | LVDS   |    | Complemental input signal of IN4                                                            |

| 56   | IN5          | LVDS   |    | Along with IN5, it is LVDS differential input from 100Hz - 8kHz signal                      |

| 57   | IN5          | LVDS   |    | Complemental input signal of IN5                                                            |

| 58   | IN6          | LVDS   |    | Along with IN6, it is LVDS differential input from 100Hz - 8kHz signal                      |

| 59   | IN6          | LVDS   |    | Complemental input signal of IN6                                                            |

| 68   | IN7          | LVDS   |    | Along with $\overline{IN7}$ , it is LVDS differential input from 100Hz - 8kHz signal        |

| 69   | IN7          | LVDS   |    | Complemental input signal of IN7                                                            |

| 70   | IN8          | LVDS   |    | Along with $\overline{\text{IN8}}$ , it is LVDS differential input from 100Hz - 8kHz signal |

| 71   | IN8          | LVDS   |    | Complemental input signal of IN8                                                            |

| 72   | IN9          | LVDS   |    | Along with IN9, it is LVDS differential input from 100Hz - 8kHz signal                      |

| 73   | IN9          | LVDS   | 1  | Complemental input signal of IN9                                                            |

| 74   | IN10         | LVDS   |    | Along with IN10, it is LVDS differential input from 100Hz - 8kHz signall                    |

| 75   | IN10         | LVDS   |    | Complemental input signal of IN10                                                           |

| 78   | IN11         | LVDS   |    | Along with IN11, it is LVDS differential input from 100Hz - 8kHz signal                     |

| 79   | IN11         | LVDS   |    | Complemental input signal of IN11                                                           |

| 80   | IN12         | LVDS   |    | Along with IN12, it is LVDS differential input from 100Hz - 8kHz signal                     |

| 81   | IN12         | LVDS   |    | Complemental input signal of IN12                                                           |

| 82   | LOOP_IN      | LVDS   |    | Along with LOOP_IN, it is LVDS differential input for loop back signal                      |

| 83   | LOOP_IN      | LVDS   |    | Complemental input signal of LOOP_IN                                                        |

| 84   | LOOP_OUT     | LVDS   |    | Complement output signal of LOOP_OUT                                                        |

| 85   | LOOP_OUT     | LVDS   |    | Along with LOOP_OUT, it is LVDS differential output for loop back signal                    |

| 86   | 0UT12        | LVDS   |    | Complemental output signal of OUT12                                                         |

| 87   | 0UT12        | LVDS   |    | Along with OUT12, it is 25MHz LVDS differential output with PWM message                     |

| 89   | 0UT11        | LVDS   |    | Complemental output signal of OUT11                                                         |

| 90   | <u>0UT11</u> | LVDS   |    | Along with OUT11, it is 25MHz LVDS differential output with PWM message                     |

| 91   | 0UT10        | LVDS   |    | Complemental output signal of OUT10                                                         |

| 92   | <u>0UT10</u> | LVDS   |    | Along with OUT10, it is 25MHz LVDS differential output with PWM message                     |

| 100  | OUT9         | LVDS   |    | Complemental output signal of OUT9                                                          |

## **Pin Descriptions continued**

| Pin#    | Name         | Туре          | 10    | Description                                                                                                         |

|---------|--------------|---------------|-------|---------------------------------------------------------------------------------------------------------------------|

| 101     | <u>0UT9</u>  | LVDS          |       | Along with OUT9, it is 25MHz LVDS differential output with PWM message                                              |

| 102     | OUT8         | LVDS          |       | Complemental output signal of OUT8                                                                                  |

| 103     | <u>0UT8</u>  | LVDS          |       | Along with OUT8, it is 25MHz LVDS differential output with PWM message                                              |

| 104     | OUT7         | LVDS          |       | Complemental output signal of OUT7                                                                                  |

| 105     | OUT7         | LVDS          | I     | Along with OUT7, it is 25MHz LVDS differential output with PWM message                                              |

| 108     | OUT6         | LVDS          |       | Complemental output signal of OUT6                                                                                  |

| 109     | OUT6         | LVDS          | Ι     | Along with OUT6, it is 25MHz LVDS differential output with PWM message                                              |

| 110     | OUT5         | LVDS          | I     | Complemental output signal of OUT5                                                                                  |

| 111     | OUT5         | LVDS          | I     | Along with OUT5, it is 25MHz LVDS differential output with PWM message                                              |

| 112     | OUT4         | LVDS          | I     | Complemental output signal of OUT4                                                                                  |

| 113     | OUT4         | LVDS          | I     | Along with OUT4, it is 25MHz LVDS differential output with PWM message                                              |

| 116     | OUT3         | LVDS          |       | Complemental output signal of OUT3                                                                                  |

| 117     | OUT3         | LVDS          | 1     | Along with OUT3, it is 25MHz LVDS differential output with PWM message                                              |

| 118     | OUT2         | LVDS          |       | Complemental output signal of OUT2                                                                                  |

| 119     | OUT2         | LVDS          |       | Along with OUT2, it is 25MHz LVDS differential output with PWM message                                              |

| 120     | 0UT1         | LVDS          |       | Complemental output signal of OUT1                                                                                  |

| 121     | 0UT1         | LVDS          |       | Along with OUT1, it is 25MHz LVDS differential output with PWM message                                              |

| 4       | DVDD33       | Power         | <br>P | 3.3V supply for digital IO                                                                                          |

| 4<br>17 | 01000        |               |       | o.ov ouppiy for digital to                                                                                          |

| 12      | DVDD18       | Power         | Р     | 1.8V supply for digital core                                                                                        |

| 20      | DVDD10       | TOWCI         | 1     |                                                                                                                     |

| 125     |              |               |       |                                                                                                                     |

| 13      | DVSS         | Ground        | GND   | Digital ground                                                                                                      |

| 21      | 5100         | around        | GND   | Digital ground                                                                                                      |

| 126     |              |               |       |                                                                                                                     |

| 24      | VDD18_FB_CAP | Power Output  | P/0   | 1.8 V internal LDO regulator de-coupling pin. Connect a 1µF decoupling                                              |

|         |              | i onor output | 170   | capacitor from this pin to ground.                                                                                  |

| 25      | VSS_FB       | Ground        | GND   | Ground for internal PLL feedback circuit                                                                            |

| 26      | VDD33_FB     | Power         | P     | 3.3V supply for Internal PLL feedback circuit LDO                                                                   |

| 37      | VSS_PLL      | Ground        | GND   | Ground for PLL                                                                                                      |

| 39      | VDD33_PLL    | Power         | P     | 3.3V supply for PLL                                                                                                 |

| 41      | VDD33_RX     | Power         | <br>P | 3.3V supply for internal LDO and REFS, REFD, LOOP_IN, and IN1 - IN12 receivers                                      |

| 51      | VDD00_IIX    | TOWER         | '     |                                                                                                                     |

| 61      |              |               |       |                                                                                                                     |

| 66      |              |               |       |                                                                                                                     |

| 77      |              |               |       |                                                                                                                     |

| 42      | VSS_RX       | Ground        | GND   | Ground for REFS, REFD, LOOP_IN, and IN1 - IN12 receivers                                                            |

| 50      |              |               |       | · · · · · · · · · · · · · · · · · · ·                                                                               |

| 60      |              |               |       |                                                                                                                     |

| 62      |              |               |       |                                                                                                                     |

| 67      |              |               |       |                                                                                                                     |

| 76      |              |               |       |                                                                                                                     |

| 65      | VDD18_RX_CAP | Power Output  | Р     | Internal LDO 1.8V output pin for regulator de-coupling. Connect a 1µF de-coupling capacitor from this pin to ground |

| 88      | VDD33_TX     | Power         | Р     | 3.3V supply for internal LDO and LOOP_OUT and OUT1 - OUT12 transmitter                                              |

| 98      | .5500_IA     |               |       |                                                                                                                     |

| 106     |              |               |       |                                                                                                                     |

| 114     |              |               |       |                                                                                                                     |

| 123     |              |               |       |                                                                                                                     |

| 93      | VSS_TX       | Ground        | GND   | Ground for LOOP_OUT and OUT1 - OUT12 transmitter                                                                    |

| 97      | -            |               |       |                                                                                                                     |

| 99      |              |               |       |                                                                                                                     |

| 107     |              |               |       |                                                                                                                     |

| 115     |              |               |       |                                                                                                                     |

| 122     |              |               |       |                                                                                                                     |

| 95      | VDD18_TX_CAP | Power Output  | P/0   | Internal LDO 1.8V output pin for regulator de-coupling. Connect a 1µF de-coupling                                   |

|         |              |               |       | capacitor from this pin to ground                                                                                   |

|         | VDD18_TX_CAP | Power Output  | P/0   |                                                                                                                     |

|         |              |               |       |                                                                                                                     |

NTC1012 Data Sheet: TM137 Page 12 Rev: 00 Date: 01/06/19

# **Pin Descriptions continued**

| Pin# | Name | Туре | IO | Description           |

|------|------|------|----|-----------------------|

| 1    | NB   |      |    | Not Internally Bonded |

| 2    |      |      |    |                       |

| 3    |      |      |    |                       |

| 22   |      |      |    |                       |

| 23   |      |      |    |                       |

| 27   |      |      |    |                       |

| 28   |      |      |    |                       |

| 29   |      |      |    |                       |

| 30   |      |      |    |                       |

| 31   |      |      |    |                       |

| 32   |      |      |    |                       |

| 33   |      |      |    |                       |

| 34   |      |      |    |                       |

| 35   |      |      |    |                       |

| 36   |      |      |    |                       |

| 38   |      |      |    |                       |

| 40   |      |      |    |                       |

| 63   |      |      |    |                       |

| 64   |      |      |    |                       |

| 94   |      |      |    |                       |

| 96   |      |      |    |                       |

| 124  |      |      |    |                       |

| 127  |      |      |    |                       |

| 128  |      |      |    |                       |

# **Register Table**

| Addr           | Name                       | Туре | Bits   | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|----------------------------|------|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00 -         | Chip ID                    | R    | 15 - 0 | 0x1012  | Chip ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x01           |                            |      |        |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x02           | Chip Revision              | R    | 7 - 0  | 2       | Chip revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x03           | Reserved                   |      |        |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x04 -<br>0x07 | Frame Size                 | RW   | 24 - 0 | 25000   | Frame size in number of cycle of 25Mhz clock                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0x07<br>0x08   | Minimum Idle Cycle         | RW   | 7 - 0  | 100     | Minimum idle cycle between PWM data and next SYNC Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x09           | Reference                  | RW   | 5 - 0  | 0x24    | [3:0] Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | Parameters                 |      |        |         | [5:4] # of SOF cycle, 0 or 1: 1, 2: 2, 3: 3                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x0a           | Dummy Cycle                | RW   | 3 - 0  | 2       | Number of dummy cycles inserted when PWM generator take the PWM message from reference. If the value < 2, it will be treated as 2. If the value > 8, it will be treated as 8.                                                                                                                                                                                                                                                                                                                 |

| 0x0b -<br>0x0c | PWM Dummy<br>Cycle Content | RW   | 15 - 0 | 0x5555  | The dummy cycle content. Every 2 bits are associated with<br>one dummy cycle the encode scheme as follows.<br>00: 25%,<br>01: 75%,<br>10: 50%,<br>11: don't use<br>The sequence of associated bits are as follows,<br>Bit[1:0] -> 1st dummy bit<br>Bit[3:2] -> 2nd dummy bit<br>Bit[3:2] -> 2nd dummy bit<br>Bit[5:4] -> 3rd dummy bit<br>Bit[7:6] -> 4th dummy bit<br>Bit[9:8] -> 5th dummy bit<br>Bit[11:10] -> 6th dummy bit<br>Bit[13:12] -> 7th dummy bit<br>Bit[15:14] -> 8th dummy bit |

| 0x0d           | Start/Restart<br>PLL       | RW   | 0      | 0       | The value change from 0 to 1 will trig PLL to re-lock the reference<br>and re-search frame SYNC position                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0e           | PLL Status                 | R    | 3 - 0  | 0       | <ul> <li>PLL status indication,</li> <li>[0] reference lock indication, 0: not locked 1: locked</li> <li>[1] frame sync position status, 0: not located, 1: located</li> <li>[2] frame sync los indication, 0: no los, 1: los</li> <li>[3] frame sync position error, 0: no error, 1: inconsistent frame sync position</li> </ul>                                                                                                                                                             |

| OxOf           | Event Status               | RW   | 5 - 0  | 0       | <ul> <li>6 different event status, if the associated status changed, the bit will be changed to 1 until the user write 1 to clear this bit,</li> <li>[0] reference lock indication changed</li> <li>[1] frame sync position status changed</li> <li>[2] frame sync los indication changed</li> <li>[3] frame sync position error status changed</li> <li>[4] phase delay calculation command is complete</li> <li>[5] frequency offset calculation command is complete</li> </ul>             |

| 0x10 -<br>0x11 | Phase Skew<br>Control      | RW   | 12 - 0 | 0       | Skew adjustment between SYNC edge and OUTx. It is a 2's complement value in ps unit. Positive value makes positive delay for OUTx, negative value makes negative delay for OUTx                                                                                                                                                                                                                                                                                                               |

| 0x12           | Reserved                   |      |        |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x13           | OUT1<br>Parameter          | RW   | 7 - 0  | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul>                                           |

| 0x14           | Reserved                   |      |        |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Addr | Name              | Туре | Bits  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|-------------------|------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x15 | OUT2<br>Parameter | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| 0x16 | Reserved          |      | 7 0   | 000     |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x17 | OUT3<br>Parameter | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| 0x18 | Reserved          |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x19 | OUT4<br>Parameter | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul>  |

| 0x1a | Reserved          |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x1b | OUT5<br>Parameter | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| Ox1c | Reserved          |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x1d | OUT6<br>Parameter | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| Ox1e | Reserved          |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ox1f | OUT7<br>Parameter | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| 0x20 | Reserved          |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Addr | Name                    | Туре | Bits  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|-------------------------|------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x21 | OUT8<br>Parameter       | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| 0x22 | Reserved                |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x23 | OUT9<br>Parameter       | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| 0x24 | Reserved                |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x25 | OUT10<br>Parameter      | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| 0x26 | Reserved                |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x27 | OUT11<br>Parameter      | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| 0x28 | Reserved                |      |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x29 | OUT12<br>Parameter      | RW   | 7 - 0 | 0x08    | <ul> <li>[3:0] is reserved</li> <li>[4] PWM data source, 0: user supply, 1: from reference</li> <li>[5] If PWM data is from user, this bit define the output PWM cycle per bit, 0: 1 cycle per bit, 1: two cycle per bit</li> <li>[6] If PWM data is from user, this bit select the LSB or MSB of transmission order in each byte, 0: LSB, 1: MSB</li> <li>[7] Transmitter on or off, 0: power down transmitter, 1: power up transmitter</li> </ul> |

| 0x2a | OUT1 FIFO<br>data port  | RW   | 7 - 0 |         | The data port for fifo dedicated for OUT1                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x2b | OUT2 FIFO<br>data port  | RW   | 7 - 0 |         | The data port for fifo dedicated for OUT2                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x2c | OUT3 FIFO<br>data port  | RW   | 7 - 0 |         | The data port for fifo dedicated for OUT3                                                                                                                                                                                                                                                                                                                                                                                                           |